字里行間:3D NAND閃存的下一個(gè)前沿

自20世紀(jì)80年代末進(jìn)入內(nèi)存市場(chǎng)以來(lái),NAND閃存從根本上改變了大量數(shù)據(jù)的存儲(chǔ)和檢索方式。

這種非易失性存儲(chǔ)器專為高密度數(shù)據(jù)存儲(chǔ)設(shè)計(jì),幾乎出現(xiàn)在電子市場(chǎng)的每一個(gè)細(xì)分領(lǐng)域,從智能手機(jī)到數(shù)據(jù)中心及介于兩者之間的各個(gè)領(lǐng)域。它被廣泛應(yīng)用于大多數(shù)可拆卸和便攜式存儲(chǔ)設(shè)備,如SD卡和USB驅(qū)動(dòng)器。近年來(lái),3D NAND在AI熱潮中也發(fā)揮了重要作用,為訓(xùn)練AI模型所需的大量數(shù)據(jù)提供了高效的存儲(chǔ)。

隨著數(shù)據(jù)存儲(chǔ)需求的爆炸式增長(zhǎng),芯片公司正競(jìng)相提高NAND閃存的單元密度,單位為每平方毫米的千兆比特(Gb/mm2),同時(shí)降低每位成本。十多年前,半導(dǎo)體行業(yè)從二維轉(zhuǎn)向三維NAND,以克服傳統(tǒng)內(nèi)存縮放的限制。近年來(lái),公司通過(guò)增加每塊芯片存儲(chǔ)單元的層數(shù)和每單元存儲(chǔ)的位數(shù)(商用NAND閃存中最多可達(dá)四個(gè)位)來(lái)提升存儲(chǔ)密度。

其中最重要的發(fā)展之一是從浮柵晶體管轉(zhuǎn)向電荷陷阱單元。浮柵技術(shù)將電荷儲(chǔ)存在導(dǎo)體中,而電荷陷阱電池則將電荷儲(chǔ)存在絕緣體中。這減少了存儲(chǔ)單元之間的靜電耦合,提高了讀寫性能。電荷捕捉電池還為更高密度打開了大門,因?yàn)樗鼈兛梢灾圃斓帽雀鸥 ?/p>

但隨著3D NAND越來(lái)越突破物理極限,半導(dǎo)體行業(yè)正轉(zhuǎn)向多項(xiàng)新技術(shù),將存儲(chǔ)單元更緊密地壓縮在一起——不僅是橫向,也包括縱向。imec開發(fā)的多項(xiàng)新創(chuàng)新實(shí)現(xiàn)了垂直擴(kuò)展,同時(shí)不犧牲內(nèi)存的性能和可靠性:氣隙集成和電荷陷阱層分離。

電荷陷阱單元內(nèi)部:3D NAND的構(gòu)建模塊

半導(dǎo)體行業(yè)計(jì)劃在未來(lái)幾年內(nèi)采用全環(huán)柵(GAA)或納米片晶體管用于邏輯芯片。但GAA架構(gòu)已經(jīng)在3D NAND閃存領(lǐng)域被廣泛使用,是高密度數(shù)據(jù)存儲(chǔ)的主力。在這種三維架構(gòu)中,存儲(chǔ)單元被堆疊成垂直字符串,單元格通過(guò)水平字線定位。

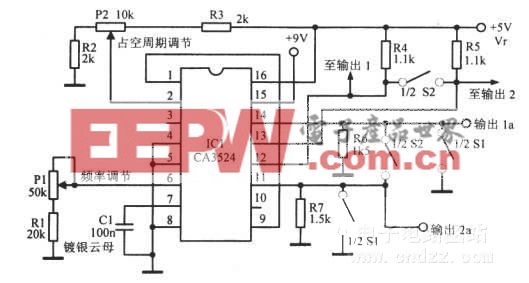

在大多數(shù)情況下,電荷捕捉單元充當(dāng)3D NAND中的存儲(chǔ)裝置。記憶單元類似MOSFET。然而,它在晶體管柵極氧化層內(nèi)嵌入了一層薄薄的氮化硅(SiN)。這使柵極氧化層變成一種稱為氧化物-氮化物-氧化物(ONO)堆疊的半導(dǎo)體材料堆,這些層分別作為阻隔氧化層、捕獲窒化物和隧道氧化層(見圖1)。

1. 圖示展示了一個(gè)3D NAND GAA架構(gòu),采用一串垂直電荷陷阱單元,具有氧化氮化物氧化物(ONO)柵極介電質(zhì)和有限數(shù)量的字線(WL)。

當(dāng)柵極偏置為正時(shí),通道區(qū)域的電子穿過(guò)氧化硅層,被困在SiN層中。這會(huì)提高晶體管的閾值電壓。電池狀態(tài)可以通過(guò)從源頭施加電壓到漏極來(lái)測(cè)量。如果電流流動(dòng),意味著沒有電子被困住,記憶單元處于表示“1”的狀態(tài)。如果沒有測(cè)量到電流,電池處于所謂的“被困電子”狀態(tài),即“0”。

電荷阱單元采用三維NAND結(jié)構(gòu),采用GAA垂直通道方法實(shí)現(xiàn)。想象將平面晶體管旋轉(zhuǎn)超過(guò)90度,而現(xiàn)在垂直的導(dǎo)通通道被柵極堆棧包圍。

GAA通道的制造過(guò)程首先是交替堆疊導(dǎo)體層(硅,作為字線)和絕緣層(氧化硅,用于分離字線)。接下來(lái),使用先進(jìn)的干式蝕刻工具在堆疊中鉆孔形成圓柱形孔。最后,在孔的側(cè)壁上交替沉積一層氧化硅和SiN,多晶硅晶體管通道位于其中心。這種布置通常被稱為通心粉通道。

下一代三維NAND:?jiǎn)卧询B與單元縮放

未來(lái)幾年,存儲(chǔ)器行業(yè)將推動(dòng)基于GAA的3D NAND閃存路線圖達(dá)到極限。

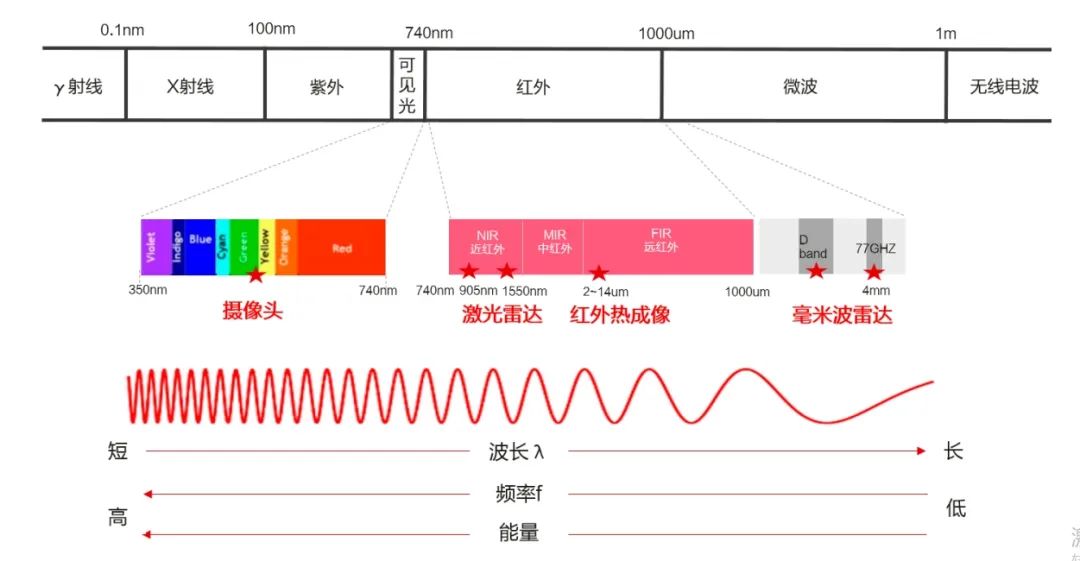

如今,主要廠商正在推出3D NAND閃存芯片,芯片層層超過(guò)300層氧化層/字線層層疊加在一起(見圖2)。這一數(shù)字還將進(jìn)一步增加,預(yù)計(jì)到2030年將達(dá)到1000層,約為100 Gbit/mm 2。挑戰(zhàn)在于如何在30微米厚的堆棧中保持弦徑大致相同。但在如此狹小的空間內(nèi)保持均勻,會(huì)導(dǎo)致更高的加工復(fù)雜性和成本,挑戰(zhàn)了高堆疊沉積和高長(zhǎng)弦比蝕刻步驟。

2. 這張3D NAND閃光燈圖突出顯示相鄰字行之間的z音高。

為了補(bǔ)充更多層疊加,半導(dǎo)體公司正在投資多種互補(bǔ)工具以提升3D NAND的存儲(chǔ)密度。這些“縮放增強(qiáng)”包括增加每個(gè)單元的位數(shù)和降低GAA單元的x-y間距(橫向擴(kuò)展)。除了位和單元密度的提升外,企業(yè)還在采取措施提升存儲(chǔ)陣列的面積效率。

另一種擴(kuò)展機(jī)制是層疊,即將閃存設(shè)備疊加以增加總層數(shù)。在3D NAND中,電池串聯(lián)形成串聯(lián),通過(guò)疊加交替的絕緣子和導(dǎo)體層并在其上鉆孔實(shí)現(xiàn)。單元堆疊過(guò)程可以重復(fù)兩到三次——未來(lái)可能再做四次——以創(chuàng)建更長(zhǎng)的芯片字符串。每組單元格有時(shí)被稱為“層級(jí)”。

通過(guò)切割大量存儲(chǔ)單元并疊放,制造更高的3D NAND芯片,企業(yè)可以在不必同時(shí)制造所有存儲(chǔ)單元的情況下增加總層數(shù)。例如,公司可以組裝250層內(nèi)存單元,然后將其中四層疊加到一塊擁有1000層的3D NAND芯片中。主要挑戰(zhàn)是如何在這些多層存儲(chǔ)芯片上刻出足夠深的孔,然后均勻填充。

此外,公司還將底層邏輯從NAND陣列中分離,并以一種稱為CMOS綁定陣列(CbA)的配置重新連接。在這種設(shè)計(jì)中,CMOS在獨(dú)立的硅晶圓上制造,然后通過(guò)先進(jìn)的封裝技術(shù),特別是混合鍵合,連接到NAND陣列。CbA是CMOS-under-Array(CuA)的下一階段,NAND是在CMOS之上制造的,作為同一整體工藝的一部分。

展望未來(lái),公司正在考慮將多個(gè)內(nèi)存陣列綁定在單個(gè)CMOS晶圓上,作為分層疊加的替代方法——甚至將多個(gè)陣列晶圓連接到多個(gè)CMOS。

為了控制不斷上漲的制造成本,imec及半導(dǎo)體行業(yè)的其他公司也在推進(jìn)垂直或“z-pitch”比例,以減少氧化層和字線層的厚度。因此,可以以可控的成本堆疊更多內(nèi)存層。

3D NAND閃存Z間距縮放的優(yōu)缺點(diǎn)

縮小內(nèi)存層之間的空間對(duì)于持續(xù)降低下一代3D NAND的成本至關(guān)重要。相鄰字行之間的音高約為40納米,Z音高縮放的目的是進(jìn)一步減少堆棧中字線和氧化硅層的厚度。這使得每堆棧高度每微米增加更多層——也就是存儲(chǔ)單元——從而帶來(lái)成本效益。

然而,如果不進(jìn)行優(yōu)化,z-音高縮放可能會(huì)對(duì)存儲(chǔ)單元的電氣性能產(chǎn)生負(fù)面影響。它可能導(dǎo)致閾值電壓降低、增強(qiáng)亞閾值擺幅以及降低保持力。此外,它還可能提高用于編程和擦除存儲(chǔ)單元數(shù)據(jù)的電壓,這不可避免地增加了功耗,降低了存儲(chǔ)單元的速度(RC延遲),并可能導(dǎo)致相鄰單元間柵間介電的介質(zhì)擊穿。

這些效應(yīng)可追溯到兩種物理現(xiàn)象,當(dāng)記憶細(xì)胞擠壓得更緊時(shí),這些現(xiàn)象變得更加顯著:細(xì)胞間干擾和側(cè)向電荷遷移。

當(dāng)字線層厚度減小時(shí),電荷陷阱晶體管的柵極長(zhǎng)度相應(yīng)縮小。因此,柵極逐漸失去對(duì)通道的控制,促進(jìn)不同電池之間的靜電耦合。

除了細(xì)胞間干擾外,記憶單元在垂直方向的縮小還會(huì)導(dǎo)致橫向電荷遷移(或垂直電荷損失):存儲(chǔ)單元內(nèi)的電荷往往會(huì)從垂直的SiN層遷移出來(lái),從而破壞保留性。

電荷阱單元有兩個(gè)幾何方向:z和x-y(x和y維度相同,因?yàn)閱卧哂袌A柱對(duì)稱性)。電荷可以雙向從存儲(chǔ)單元泄漏。雖然電荷會(huì)沿 x-y 方向通過(guò)隧道逸出,或阻擋柵極中的氧化物,但也可能在 z 方向離開電池,最終落入相鄰電池內(nèi)部或過(guò)于靠近。這是由于橫向電荷遷移,隨著細(xì)胞垂直尺度增加、彼此距離越來(lái)越近,側(cè)向電荷遷移的重要性會(huì)增加。

接下來(lái),我們討論了能夠解決這些缺陷的技術(shù)賦能,使研究人員能夠解鎖未來(lái)3D NAND閃存的z-pitch縮放功能。

線路之間:整合空氣間隙以減少電池干擾

在相鄰字線之間整合空氣間隙是解決單元間干擾問(wèn)題的一個(gè)潛在方案。這些氣隙介電常數(shù)低于柵間介質(zhì),減少了存儲(chǔ)單元之間的靜電耦合。這是平面二維NAND閃存架構(gòu)中廣泛使用的技巧。但將空氣間隙整合進(jìn)高大的硅氧化物/字線堆棧則更具挑戰(zhàn)性。

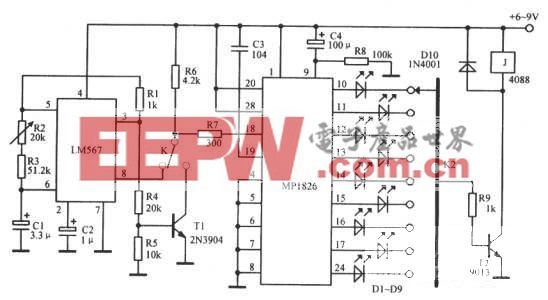

為克服這些復(fù)雜性,imec在2025年IEEE國(guó)際內(nèi)存研討會(huì)(IMW)上展示了一種獨(dú)特的集成方案,能夠精確控制字行間隙的位置。

在3D NAND中,薄層氧化硅片既被放置在存儲(chǔ)單元的柵極內(nèi)——作為分隔字線與晶體管通道的“柵介質(zhì)”——又放置在不同存儲(chǔ)單元的字線之間——作為“柵間介質(zhì)”,將相鄰的單元分隔開(見圖3)。柵極介質(zhì)形成了ONO堆棧的隧道層和阻斷層,并包圍著電荷阱SiN層。

3. 展示氣隙(a-d)的三維積分過(guò)程流程,以及透射電子顯微鏡(TEM)和能量色散X射線光譜(EDS)對(duì)氣隙(e-f)的圖像。

因此,硅氧化物不僅存在于每個(gè)存儲(chǔ)單元內(nèi)部,也存在于存儲(chǔ)單元之間。由于3D NAND存儲(chǔ)單元的制造方式,門介質(zhì)會(huì)連續(xù)從一個(gè)單元延伸到另一個(gè)單元,并且在相鄰存儲(chǔ)單元之間的空間中與柵間介質(zhì)相交。IMEC確定這是放置氣隙的理想位置。然而,用現(xiàn)有工藝技術(shù)去除(或切除)電池間的電荷阱SiN層是一項(xiàng)巨大挑戰(zhàn)。

在imec,我們找到了一種新方法,可以在不切出SiN的情況下整合氣隙。該創(chuàng)新通過(guò)在沉積ONO堆棧前,將門間硅氧化物嵌入內(nèi)存孔區(qū)域內(nèi)引入氣隙。氣隙與字線自對(duì)齊,實(shí)現(xiàn)非常精準(zhǔn)的布置。該方法也具有潛在的可擴(kuò)展性,這也是其他提出解決方案的主要問(wèn)題。阿拉伯?dāng)?shù)字

研究顯示,帶有氣隙的設(shè)備對(duì)鄰近小區(qū)干擾的敏感度低于無(wú)氣隙的設(shè)備。這是基于對(duì)未選定柵極施加所謂通電電壓時(shí),具有氣隙器件的閾值電壓較小變化得出的結(jié)論(見圖4)。結(jié)果是在一臺(tái)30納米間距下字線層有限的測(cè)試器件(門長(zhǎng)15納米,硅氧化硅柵間介電質(zhì))和直徑80納米的記憶孔上獲得的。

4. 帶氣隙(左)和無(wú)氣隙的電荷陷阱器件在不同通行電壓(右)時(shí)的閾值電壓變化。

IMEC的研究人員還研究了空氣間隙對(duì)記憶性能和可靠性的影響。氣隙不影響內(nèi)存作,支持長(zhǎng)達(dá)1000個(gè)程序/擦除周期的耐久,與無(wú)氣隙設(shè)備相當(dāng)。

基于這些結(jié)果,孔側(cè)氣隙集成被認(rèn)為是實(shí)現(xiàn)未來(lái)Z間距縮放的關(guān)鍵步驟。

電荷陷阱切割:它在閃存未來(lái)中的位置

IMEC 已經(jīng)證明可以在柵間介質(zhì)層中引入氣隙。然而,這些記憶細(xì)胞中的空洞目前在阻斷氧化物之前就已停止。如果我們能更深入地鉆入記憶單元,在阻擋氧化層和電荷陷阱層區(qū)域引入氣隙,會(huì)怎樣?

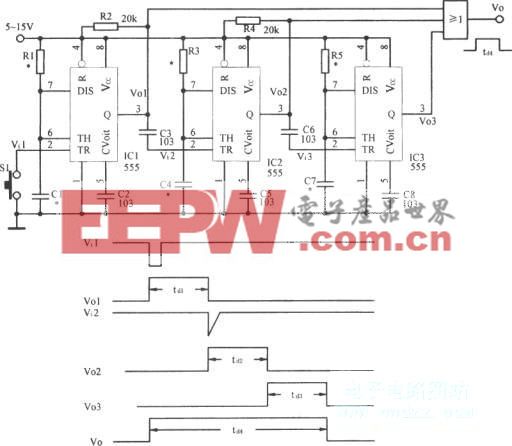

我們?cè)谀M中測(cè)試了該方法,并證明了這種電荷陷阱層分離(或電荷陷阱切割)可以增加單元的存儲(chǔ)窗口(見圖5)。此外,電荷陷阱切斷可以防止存儲(chǔ)單元內(nèi)被困的電荷橫向遷移,穿過(guò)沿氧化物/字線堆棧從上到下排列的SiN串。

5. 連續(xù)柵極堆棧(左)與帶有電荷捕捉層切割和氣隙積分的柵極堆棧(右)之間的區(qū)別。

通過(guò)編程閾值電壓到不同電平,數(shù)據(jù)存儲(chǔ)在閃存單元中。存儲(chǔ)單個(gè)比特時(shí),單元需要兩個(gè)電平:例如0伏和1伏。存儲(chǔ)2位時(shí),單元需要四個(gè)電平:例如:0 V、0.5 V、1 V和1.5 V。隨著位數(shù)增加,電壓水平也隨之上升。

需要增加閾值電壓的總范圍(內(nèi)存窗口),或減少相鄰電平之間的間隔(1位時(shí)間隔1伏,2位時(shí)0.5伏)。但當(dāng)這些電壓水平距離更近時(shí),區(qū)分它們的差異會(huì)變得更加困難。通過(guò)增加存儲(chǔ)窗口,電荷陷阱切割可以幫助每個(gè)單元實(shí)現(xiàn)更多級(jí)別——從而增加比特?cái)?shù)。

但在3D NAND閃光燈中集成切割的電荷陷阱并非易事,因?yàn)樗枰ㄟ^(guò)極深且狹窄孔的側(cè)壁進(jìn)行定向蝕刻和沉積。對(duì)于這些結(jié)構(gòu),2D NAND閃存所用的技術(shù)工具箱已無(wú)法滿足需求。目前,imec正與供應(yīng)商合作開發(fā)新技術(shù),以實(shí)現(xiàn)可控切斷該電荷陷阱。

一旦電荷捕捉層能夠中斷,imec 計(jì)劃將其與氣隙集成方案結(jié)合,提供完整且可擴(kuò)展的 z 螺距擴(kuò)展解決方案。

“切割”3D NAND閃存的復(fù)雜性

隨著半導(dǎo)體行業(yè)競(jìng)相在更小空間內(nèi)存儲(chǔ)更多數(shù)據(jù),3D NAND閃存的z-pitch擴(kuò)展正成為管理與內(nèi)存層數(shù)量增加相關(guān)成本的關(guān)鍵。基于其長(zhǎng)期的處理專長(zhǎng)和強(qiáng)大的設(shè)備供應(yīng)商生態(tài)系統(tǒng),imec正在開發(fā)支持激進(jìn)z-pitch縮放同時(shí)保持內(nèi)存運(yùn)行和可靠性的關(guān)鍵技術(shù):氣隙集成和電荷陷阱切斷。

與此同時(shí),傳統(tǒng)電荷阱單元架構(gòu)的提升開始放緩,內(nèi)存密度的提升可能會(huì)在本十年末前逐漸減弱。因此,研究人員正在認(rèn)真審視更激進(jìn)的單元架構(gòu),以推動(dòng)內(nèi)存路線圖延續(xù)到2030年之后。一種提出的三維方法重新構(gòu)想了整個(gè)布局,將記憶單元的導(dǎo)電通道水平排列,而非垂直排列。

另一種方法,imec于2023年評(píng)估,電荷陷阱存儲(chǔ)單元通過(guò)溝槽架構(gòu)連接,而非將單元集成為圓形GAA幾何結(jié)構(gòu),有望實(shí)現(xiàn)比特存儲(chǔ)密度的飛躍。

所有這些發(fā)展表明,目前正在開發(fā)的多項(xiàng)技術(shù)將使內(nèi)存行業(yè)逐步向100 Gb/mm 2的數(shù)據(jù)存儲(chǔ)轉(zhuǎn)變——這一需求主要由云計(jì)算和人工智能應(yīng)用驅(qū)動(dòng)。

評(píng)論