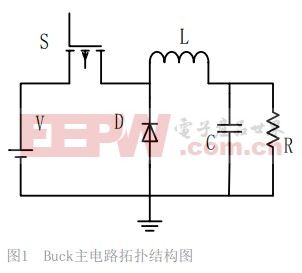

Buck電路EMI優(yōu)化實例

LED驅(qū)動的CISPR5傳導(dǎo)測試

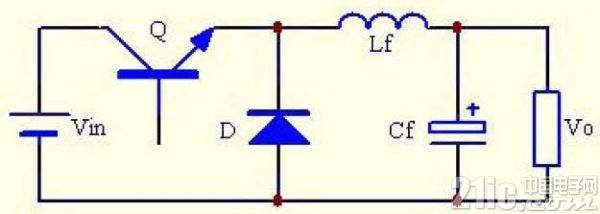

如圖14.36,為一個BUCK電路的LED驅(qū)動板,從原理圖來看,綠色的濾波器輸入地和黃色的功率地通過輸入電容隔開,這樣高頻電流環(huán)路的噪聲電流會先經(jīng)過輸入的陶瓷電容,但是實際的PCB布局中,可以看到輸入地和高頻電流環(huán)路重合,噪聲可以直接耦合到輸入環(huán)路上。

圖 14.36 一個BUCK電路的布局

我們實際測得結(jié)果如圖14.37(a),二次諧波的幅值比一次諧波還要高很多,并超過了限值。為了解決這個耦合問題,我們需要調(diào)整輸入地的位置,原將輸入地和功率地斷開,移到右側(cè),通過過孔和輸入陶瓷電容連接。可以看到,如圖14.37(b),二次諧波的分量下降了將近20dB。

(a) (b)

圖 14.37 布局優(yōu)化前后對比

但是可以看到傳導(dǎo)高頻78~108M附近的噪聲幅值還比較高,遠(yuǎn)超過CISPR5 class 5限值要求。這部分的噪聲通常主要來自共模電流,需要對板上的dv/dt引起的電場進(jìn)行優(yōu)化。

按照前面的分析思路,可以通過減小SW面積和電感體積進(jìn)行噪聲源的抑制。10μH的電感以及SW鋪銅面積都比較大,在保證電流能力的情況下,切掉部分SW面積,換用更小體積的小感值電感。最終結(jié)果如圖14.38所示,優(yōu)化SW面積和電感后,提升了10dB左右,基本滿足了class 5的限值要求。

圖 14.38 優(yōu)化SW面積和電感及提升結(jié)果

評論