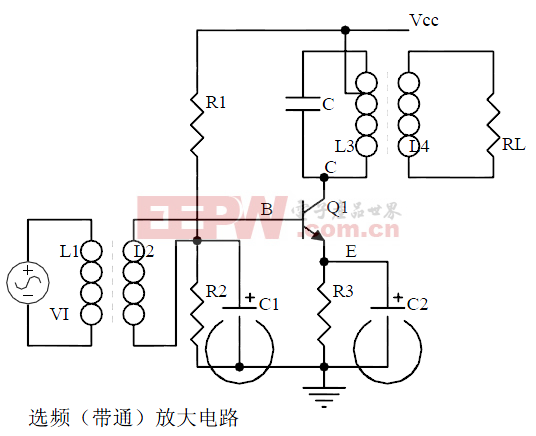

如何設計一個放大電路(2)噪聲

放大系統降噪的核心思路是 “抑制內部固有噪聲 + 阻斷外部干擾噪聲”,需結合元器件選型、電路拓撲、布線屏蔽等多維度措施,以下是結構化、可直接落地的解決方案:

一、 抑制內部固有噪聲(器件與電路層面)

內部噪聲由放大器件(晶體管、運放)、無源元件(電阻)本身產生,是系統的本底噪聲,決定了降噪的下限。

元器件選型優化

由于經典的模電教材、文檔往往都是由ADI、TI這樣芯片設計公司的專家寫的,他們更多的視角是器件本身。所以大量的文檔篇幅都是描述器件本身的評估。

估算的方法很多教材和文檔都有描述,我這里就先不展開。我們后續內容再展開。

一個不可回避的事實就是:我們實際設計出來的電路的噪聲遠遠大于評估噪聲。這是什么原因呢?

因為除了器件自身的噪聲之外,跟我們的設計有很大的關系。

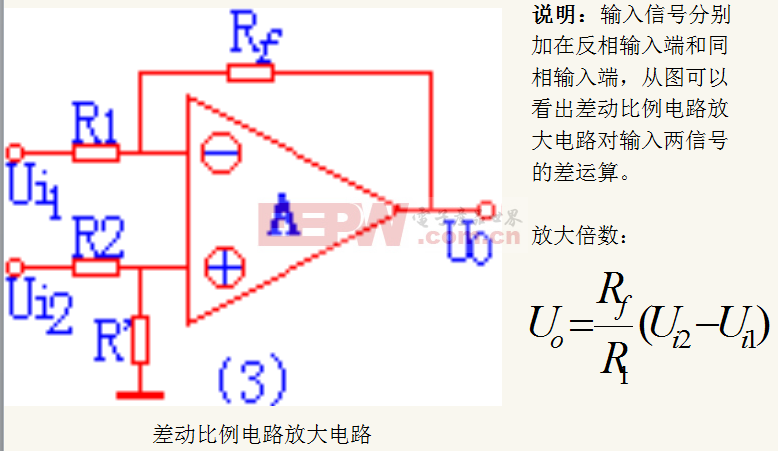

電路拓撲與增益分配優化

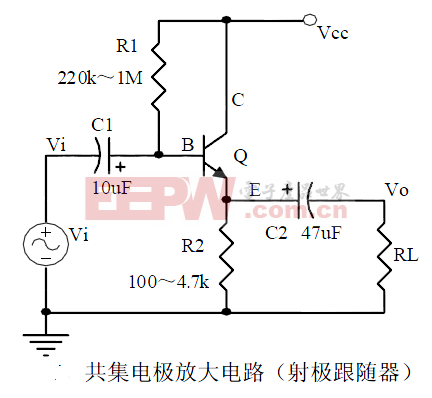

晶體管電路: 射極跟隨器(共集電極)噪聲系數低于共射放大;共射放大可加射極電阻負反饋降低噪聲。

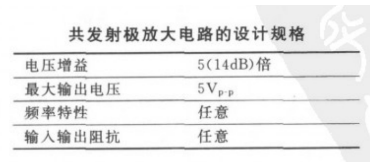

運放電路: 同相放大的噪聲增益更低(噪聲增益 Gn=1+R1Rf ),優于反相放大(噪聲增益等于信號增益)。

決定(噪聲系數級聯公式: Ftotal≈F1+G1F2?1 ),前級要 低噪聲 + 適度增益(如 10~20 倍),后級負責提升總增益,不貢獻額外噪聲。

Pn∝Δf ),用 RC 低通或有源濾波器,將帶寬限制在 信號最高頻率的 1.2~1.5 倍,濾除帶外噪聲。

反饋網絡降噪反饋電阻的噪聲會被放大,需選低噪電阻,且阻值不宜過大;可在反饋電阻并聯小電容,形成極點抑制高頻噪聲。

二、 阻斷外部干擾噪聲(系統與布線層面)

外部噪聲是放大系統的主要干擾來源,包括電源紋波、電磁干擾(EMI)、接地噪聲等,需通過 “隔離 + 屏蔽 + 濾波” 切斷干擾路徑。

1、電源噪聲抑制

1.1 選擇PSSR更好的運放

運放的電源抑制比(PSSR,Power Supply Rejection Ratio)是衡量其抑制電源電壓波動對輸出影響能力的核心指標,數值越高(單位為 dB),電源噪聲抑制效果越好。高 PSSR 運放的設計核心是切斷或衰減電源噪聲向輸出端的耦合路徑,主要通過電路架構優化、模塊設計改進、工藝選型、頻率補償四個維度實現,具體原理如下:

一、 輸入級電路架構優化:阻斷噪聲耦合的第一道防線

運放的電源噪聲主要通過輸入級偏置電路和有源器件的襯底 / 寄生電容耦合到信號通路,高 PSSR 運放的輸入級設計重點是降低這種耦合效率。

共柵管的輸出阻抗極高,大幅降低了電源電壓波動對差分對漏極電壓的影響;

同時抑制了 密勒效應,減少寄生電容帶來的高頻噪聲耦合。

采用共源共柵(Cascode)差分輸入結構

普通差分輸入級的晶體管直接連接電源,電源電壓波動會直接改變晶體管的工作點(如漏極電流、跨導),進而影響差分對的輸出。共源共柵結構在差分對上方疊加一級共柵管,相當于給輸入級增加了一個 “隔離層”:

穩定的偏置電路設計輸入級的偏置電流決定了差分對的跨導和工作穩定性,高 PSSR 運放普遍采用帶隙基準(Bandgap Reference)或電流鏡偏置,而非簡單的電阻分壓偏置:

電流鏡采用匹配性極佳的晶體管對,抵消電源波動對偏置電流的影響,避免偏置變化導致的信號失真。

帶隙基準的輸出電流 / 電壓幾乎不受電源電壓波動影響(電源抑制比可達 100dB 以上),確保差分對的偏置電流穩定;

差分輸入的對稱設計對于雙電源供電的運放,采用完全對稱的差分輸入級,讓正負電源的噪聲在差分對中相互抵消。例如,正負電源的波動幅度相同時,差分對的兩個輸入端受到的影響一致,最終輸出的差值為零,實現噪聲抵消。

1.2 增益級設計:提升增益間接增強電源抑制能力

PSSR 與運放的開環增益直接相關,核心公式為:

在相同的電源噪聲(ΔVCC)下,開環增益越高,輸出端的噪聲(ΔVOUT)越小,PSSR 數值越大。高 PSSR 運放的增益級設計主要有兩個方向:

1.3 集成內部穩壓 / 去耦模塊:從源頭過濾電源噪聲

部分高性能高 PSSR 運放(如精密運放、低噪聲運放)會在芯片內部集成微型 LDO(低壓差穩壓器)或去耦電容,直接對外部輸入的電源進行預處理:

1.4 工藝與寄生參數優化:減少非理想因素的影響

芯片制造工藝和版圖設計的非理想因素(如襯底耦合、寄生電容 / 電感)會顯著降低運放的高頻 PSSR,高 PSSR 運放的工藝優化重點如下:

1.5 頻率補償設計:保證寬頻段的 PSSR 穩定性

PSSR 是頻率相關參數:低頻段運放開環增益高,PSSR 數值大;高頻段開環增益下降,PSSR 會隨之降低。高 PSSR 運放的頻率補償設計目標是拓寬高 PSSR 的頻率范圍:

電源引腳和信號引腳分開布局,避免電源噪聲通過布線的寄生電容耦合到信號通路;

差分對晶體管采用 匹配性版圖設計(如共質心布局),降低工藝偏差導致的電源噪聲抑制能力下降;

增加電源地線的寬度,降低地線阻抗,減少電源波動的幅度。

采用 米勒補償或超前 - 滯后補償,在保證運放相位裕度的前提下,優化開環增益的頻率響應,避免在關鍵頻段(如 10kHz-1MHz)出現 PSSR 的 “低谷”;

增加高頻去耦網絡,針對開關電源等高頻噪聲源,提升特定頻段的噪聲抑制能力。

采用 SOI(絕緣體上硅)工藝

傳統體硅工藝中,晶體管的襯底直接接地,電源噪聲會通過襯底的寄生電阻 / 電容耦合到有源器件。SOI 工藝采用絕緣層將襯底與器件隔離,徹底切斷襯底耦合路徑,大幅提升高頻 PSSR(尤其是 1MHz 以上頻段)。

優化版圖布局與布線

內部 LDO 穩壓

LDO 的作用是將外部波動的電源電壓轉換為穩定的直流電壓,再供給運放的核心模塊(輸入級、增益級)。外部電源的噪聲會被 LDO 的反饋環路抑制,核心模塊相當于工作在 “干凈” 的電源下,從源頭消除噪聲耦合。

片內集成去耦電容

在電源引腳與地之間集成 pF 級的片內去耦電容,用于濾除高頻電源噪聲(如開關電源的紋波)。相比外部去耦電容,片內電容的寄生電感更小,高頻濾波效果更好,能有效抑制 MHz 級別的電源噪聲。

多級增益級聯 + 折疊式共源共柵結構單級增益級的增益有限(通常 30-40dB),高 PSSR 運放采用2-3 級增益級聯,并在每一級采用折疊式共源共柵結構,將開環增益提升至 80-120dB,大幅提升電源噪聲抑制能力。

避免增益級直接耦合電源增益級的晶體管采用電流源負載替代傳統的電阻負載,電流源的輸出阻抗遠高于電阻,不僅能提升增益,還能降低電源波動對負載電壓的影響,進一步阻斷噪聲通路。

2、分級濾波去耦

每級放大電路的電源引腳旁并聯 0.1μF 陶瓷電容 + 10μF 電解電容

,陶瓷電容濾高頻噪聲,電解電容濾低頻紋波;多級放大的各級電源分開濾波,避免串擾。并且采用RC做電源濾波。

優選低紋波供電:用線性穩壓器(LDO) 代替開關電源(開關電源高頻紋波大);若必須用開關電源,需加 EMI 濾波器和 LC 濾波電路(如 10μH 電感 + 100μF 電容)。

輸入信號線 短、粗、直,遠離功率線、數字信號線(如 MCU 的 IO 線),間距大于 3 倍線寬。

敏感信號線(如前級輸入線)采用 屏蔽線,屏蔽層單端接地(兩端接地會形成接地環路)。

前放是易受干擾電路,我們要考慮其他電路對他的干擾。即需要考慮容性耦合,也需要考慮感性耦合。基本分析的過程跟我們之前內容分析開關電源的環路部分是一個原理。

接地策略:低頻放大(10MHz)用多點接地**,縮短接地路徑。

放大系統的 前級輸入部分放入金屬屏蔽盒(如鋁盒),屏蔽盒可靠接地,阻擋外部電磁輻射(如電機、繼電器、射頻信號)。

若外部有強干擾源(如掃地機器人的電機、無人機的電調),需對干擾源單獨屏蔽,并做好接地。

隔離技術當存在地電位差或強干擾時,采用光電隔離或磁隔離放大器,將輸入信號與放大電路完全隔離,切斷干擾傳導路徑。

溫度控制:電阻熱噪聲、晶體管噪聲隨溫度升高而增大,精密放大系統需遠離熱源(如功率管、電源模塊),必要時加散熱片或恒溫措施。

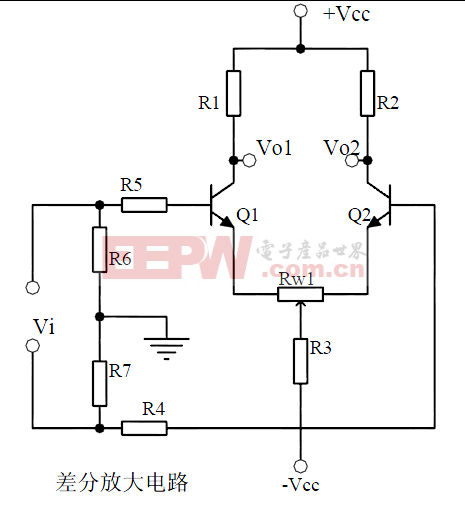

差分放大抑制共模噪聲:對于存在共模干擾的場景(如長線傳輸信號),用差分放大電路(如儀用放大器 AD620),利用共模抑制比(CMRR)抑制共模噪聲。

評論