深入理解LVDS失效保護電路

最近幾年,低壓差分信號(lvds)[1]的高速數據互連已廣泛應用于消費電子產品、高速計算機外設、通信/網絡以及無線基站等各個領域。lvds在性能、功耗、噪聲、emi以及成本等方面具有顯著優勢。采用正確的設置,lvds信號可以通過一對兒雙絞線電纜提供100mbps至800mbps的數據速率,傳輸距離為10m至15m,在pcb引線上的傳輸距離> 1m。100負載的功耗僅為1.2mw,與頻率無關。

本應用筆記主要討論lvds失效保護電路,這對于lvds正確工作非常重要。將檢驗三種失效保護電路,并分析它們的特性進而為提供應用指導。

lvds的基本特性和優點

首先簡單回顧一下lvds信號的基本特性和電路配置。圖1所示為簡單的lvds發送、接收基本電路,接收器是一個絕對轉換門限約為50mv的比較器。傳輸媒介,無論是電纜還是pcb引線,都設計成100差分阻抗。圖2 所示為媒介信號的共模和差分電平。在圖1和圖2中,vid是lvds接收器的輸入差分電壓,vod是lvds發送器的差分輸出電壓,vcm是共模電壓。

圖1. lvds的tx、rx基本電路圖

圖2. lvds信號的共模和差分電壓 電流源恒定驅動兩條緊密耦合的電纜線或pcb引線,媒介中的共模電流、電壓不隨時間改變,差分信號隨時間變化。通常,數據傳輸速率主要受負載寄生電容、電感的限制。對于圖1所示lvds電路,驅動器(發送器)的共模阻抗大部分來自負載電容。另一方面,寄生電感主要來自芯片或負載引線,而不是匹配傳輸線。此外,寄生電感值相對較小,因此對信號完整性的影響可忽略不計。由于負載共模電壓不變,負載寄生電容的影響可以忽略。因此,lvds信號與cmos或ttl信號相比能夠提供更高的數據傳輸速率。

由于兩條電纜或引線緊密耦合,因此emi僅受共模信號的影響。傳輸過程中的共模變化可以忽略,意味著lvds即使在非常高的工作頻率下也具有非常低的輻射。此外,在350mv低差分電壓擺幅在100終端電阻上僅消耗1.2mw功率,該數值保持固定,與數據速率無關。與功耗較高的單端信號(如cmos和ttl)相比,lvds信號的突出優勢是具有極低功耗。

本文引用地址:http://cqxgywz.com/article/21412.htm

失效保護功能

大多數lvds接收器都需要具有內部或外部失效保護電路,以便在特定鏈路狀態下或出現故障時接收器的輸出能具有一個已知狀態,通常為邏輯高電平。以下列出了需要失效保護的鏈路狀態或故障。

輸入開路:如果lvds芯片具有多個接收端口,則未使用的接收器輸入必須保持開路狀態,且輸出應為穩定的邏輯高電平。

輸入浮空:如果lvds驅動器處于三態、驅動器斷電或鏈路斷開,lvds必須具有穩定的邏輯高電平輸出。

輸入短路:如果兩條平行lvds電纜或引線短路,即出現連接故障,輸出應為邏輯高電平。

設計人員還希望即使在噪聲環境下也具有強大的失效保護功能,并要求它對正常狀態下的lvds工作影響最小,可忽略不計。

失效保護電路及其性能分析

這里給出了三種基本的失效保護電路:外部偏置電路、內部通道電路以及并聯電路。下面將逐一介紹這些失效保護電路的工作原理,并分析各自的優缺點。

外部偏置失效保護電路

該失效保護電路由接收器輸入引腳的三個外接電阻組成(圖3)。

圖3. 外部失效保護電路

在上述電路中,線路未被驅動時,偏置電路設置兩個輸入引腳之間的正偏移電壓,以便接收器輸出處于邏輯高電平。偏移電壓vid可由下式決定:

電路的共模電壓由下式確定:

![]()

該失效保護電路已廣泛用于早期的lvds接收器。由于具有下列優勢,所以成為首選方案:

可按照浮空傳輸線的噪聲電平靈活設置偏移電壓。

提供了一個共模返回通道和一個esd放電通道。

但是,這種方法還存在以下幾個缺點,限制了它在目前lvds應用中的使用:

兩個必要的外部電阻對于單個lvds鏈路可能不是負擔,但在采用多個鏈路時,特別是多通道應用中,就需要認真考慮。

目前,計算機外設和網絡互連的lvds數據傳輸速率達到800mbps,甚至2gbps。在如此高的數據速率下傳輸,由vid偏移量造成的不平衡接收門限會導致占空比嚴重失真,并增大抖動。

由于vid偏移不能設置過高,因此對于差分噪聲的失效保護具有較低余量。

輸入短路時該電路不起作用。電源短路時,vid偏移電壓也被短路,lvds輸出不確定。

內部通道失效保護電路

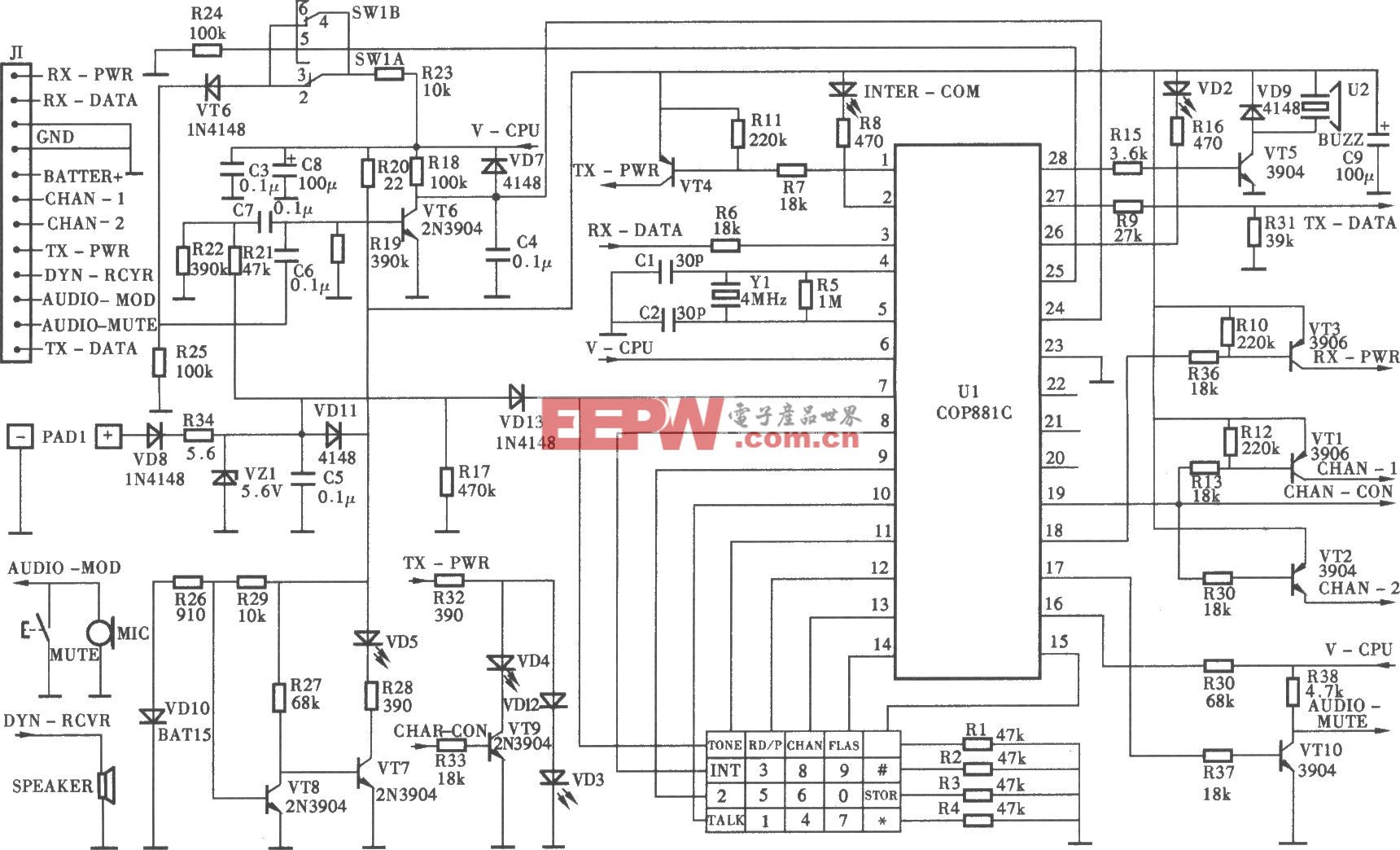

內部通道失效保護電路的設計與外部偏置電路類似,只是該電路將r1和r2集成在lvds接收器內部,使vid的偏移量成為一個內置電壓源。這種電路已廣泛用于lvds接收器[2],圖4給出了等效電路。

圖4. 內部通道失效保護電路框圖 進行內部通道電路設計時,選取r1和r2的值,使vid的內部偏移量在30mv與50mv之間。即使輸入短路,仍有正的vid偏移,這樣,在上述三種狀態下或需要失效保護時,都能夠將輸出置為邏輯高電平。

這種內部通道設計方法優于外部偏置電路,因為它克服了后者的一些缺點。內部通道失效保護電路的特性如下:

無需外部電阻。

輸入短路時仍具有保護功能。

雖然如此,內部通道失效保護在某些應用中仍具有一些缺點:

不具有設置電壓偏移的靈活性。

產生了一個不平衡的接收器門限,使占空比降低,抖動增加。

對“內部通道” 噪聲具有較低余量。

并聯失效保護電路

maxim的大多數lvds產品采用了并聯失效保護電路[3]。該電路克服了前兩種失效保護電路缺點,如圖5所示。

圖5. 并聯失效保護電路原理圖 如圖5所示,比較器監視電源電壓,并將其與vcc - 0.3v基準電壓進行比較。如果電源電壓高于基準電壓,輸出為邏輯高電平。然后,這個邏輯高電平通過一個“或”門屏蔽接收器輸出,開啟失效保護電路。在上述需要失效保護的三種特定情況(開路、浮空和短路)下,這種架構能將lvds輸出拉至邏輯高電平。只要共模電壓低于基準電壓vcc - 0.3v,這種保護方式就能正常工作。

并聯失效保護電路與傳統方案相比具有一些獨特優點:

無論對于共模還是差模信號,都具有更高的噪聲余量。

結構對稱,不會影響輸入差分信號的占空比,也不會引起抖動。

盡管具有獨特的優勢,但采用這種并聯設計仍然存在一些問題。對于多點或遠距離點對點通信,共模負載電容相對較大。發生故障時,這種電路需要一段時間使共模電壓達到vcc

- 0.3v,這樣,失效保護功能也會增加一個延遲。

結論

本應用筆記主要討論了外部偏置、內部通道和并聯電路三種不同的失效保護電路設計、工作方式及其優缺點。可以看出,對于lvds失效保護電路沒有一個十分理想的解決方案。然而,分析顯示并聯方式相對于其它兩種方案具有更多優勢。

評論