從4004到core i7——處理器的進化史-CPU構成零件-3

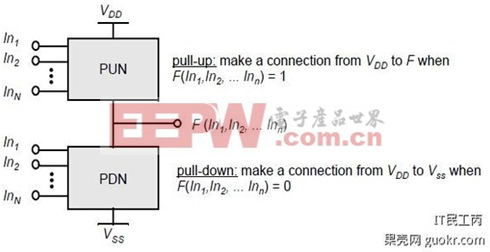

從上面的帖子中我們看到了CMOS工藝下的反相器。如果用一張圖總結一下這種設計模式就是下面的這張圖

本文引用地址:http://cqxgywz.com/article/221762.htm

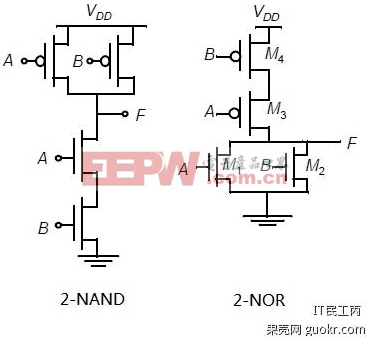

注意,上面的圖片中的PUN(pullup network)和PDN(pulldown network)是互補的,也就是說:同一組輸入下,要么PUN中存在VDD->輸出點的通路,要么PDN中存在輸出->地(VSS)的通路,這也正是互補(complementary)的含義。由于不存在由VDD->地的回路,所以CMOS邏輯電路沒有靜態功耗。我們說CMOS邏輯電路是靜態(static)的,即在一組輸入下穩定后,輸出點是通過一條低阻的(導通的MOS管的電阻大約在10k~100k數量級)通路上拉到VDD或下拉到地的。由于這樣的低阻通路是存在的,所以CMOS電路受外界干擾較小,特別受漏電的影響較小(因為電源能向其補充失掉的電荷),這使得CMOS數字電路成為最穩定、最可靠的電路之一。下面我貼兩張最常用的邏輯門:2輸入NAND和2輸入NOR的CMOS實現:

下面的內容是最后的背景知識。

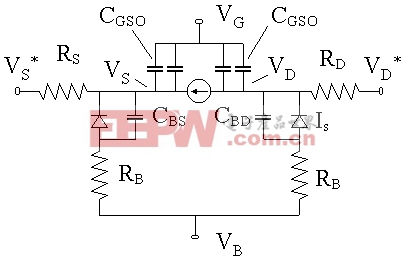

所有以上的分析中我們都在討論電路的靜態特性,即輸入穩定相當長的時間后與輸出的關系。而在IC的設計中,我們不僅僅關心一個電路功能的正確性(correctness),健壯性(robustness)還關心其性能(performance),即其在單位時間內正確地處理的輸入信息量的多少。為此我們不得不引入MOSFET管的一些細節以討論其動態特性(dynamic behavior),看看下面這張稍顯復雜的圖。

注意圖中的六個電容。這些電容是MOSFET管的寄生參數(parasitic parameter),它們的引入不可避免的,因為相鄰的導體之間必然會產生電容。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論