藍牙HCI-UART主控制接口的FPGA設計與實現

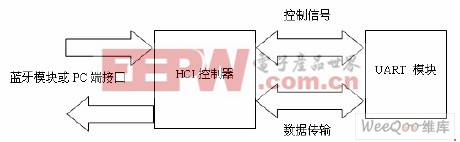

主機與藍牙模塊之間使用指令——應答的方式進行通信,主機向主機控制器發送指令分組,主機控制器執行某一指令后,大多數情況下會返回給主機一個指令完成事件分組,該分組攜帶有指令完成的信息。如果指令分組參數有誤,返回的指令狀態事件分組就會給出相應的錯誤代碼。主機與主機控制器間的數據交換則通過數據分組實現。主控制器系統原理框圖如圖2 所示。

圖2

3.1 UART 的設計

UART 的設計主要包括三個部分:發送器、接收器和波特率發生器,設計采用分模塊完成[10]。

(1)波特率發生器:

UART 的數據接收和發送是通過對波特率的設置進行實現的。波特率發生器采 用分頻器實現,分頻得到一個頻率為波特率16 倍的波特率時鐘clk_baud,分頻數N 計算公式如(1)所示, 其中clk_sys 表示系統時鐘,baudrate 為UART 的波特率。

(2)發送器模塊:

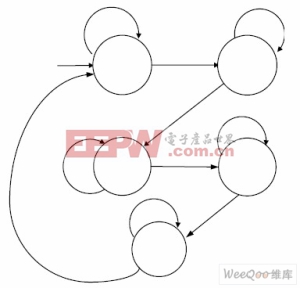

檢測到發送信號時,裝載數據,根據數據產生奇偶校驗位,按通信協議幀的格式的要求依次發送起始位、數據位、奇偶校驗位和停止位,并產生各種控制信號。整個發送過程采用有限狀態機實現,分成五個狀態(空閑idle,發送起始位send_start,發送數據send_data,發送奇偶校驗位 send_parity,發送停止位send_stop),具體過程如圖3 所示。

圖3 發送器狀態圖

評論