基于FPGA的快速9/7整形離散小波變換系統

2.2 列變換過程

由于列變換是針對行變換后的數據進行的,即對上面6片RAM中存儲的行變換后的數據進行列變換,為了提高運行速度,本文采用基于行的列變換方法,即當小波變換進行到第5行時,列變換也同時進行,第5行行變換結束時,也完成了針對第5行數據的列變換,當第6行進行小波變換時,不進行列變換操作,直到第7行小波行變化數據輸入時,再同時進行列變換計算操作,依次完成小波列變換。對于列小波變換后的低頻數據dLLl,要輸入RAM緩存以進行下一級變換,對于其他的高頻數據(dLHl,dHLl,dHHl)可以直接輸出到片外存儲器中。

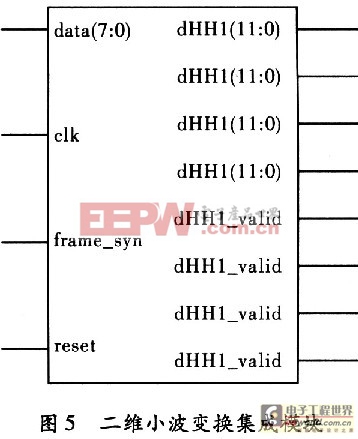

下面是設計的一級二維小波變換的集成模塊,如圖5所示。

3 仿真與綜合

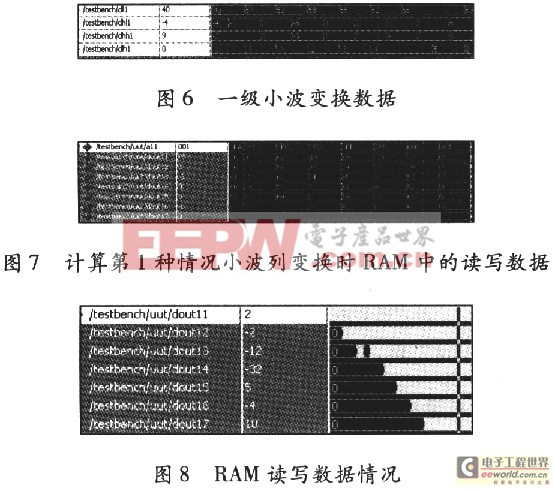

為了驗證本文設計系統的性能,使用Modlesim6.3仿真軟件對系統進行了仿真測試,下面是采用大小為1 024×1 024,圖像數據為8位的測試圖像進行測試仿真的部分波形圖。

評論