基于FPGA的PCI總線接口原理研究與設計

● 時序控制

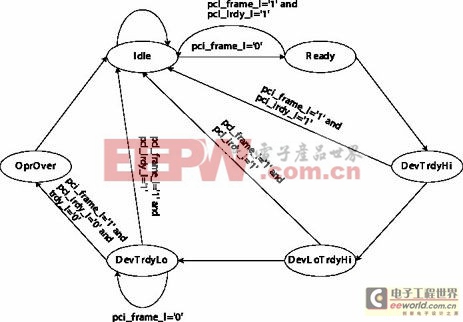

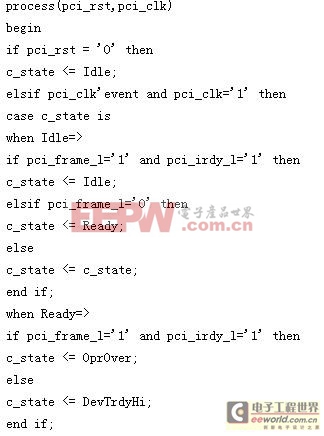

在時序控制程序中采用狀態機模型來實現不同時序的轉換。各種命令、數據交換、控制均在狀態機的管理下進行工作。PCI總線上的信號是并行工作的,因此,對應每個狀態必須明確其執行的任務。這些任務要用VHDL的進程語句來描述所發生的事件。本設計中的狀態機共使用了6種狀態,它以從設備響應狀況為依據,主要以DEVSEL#信號和TRDY#信號的狀況為依據。狀態機如圖1所示,分別對應空閑狀態(此狀態DEVSEL#、TRDY#和STOP#以及其他輸出信號為高阻態);準備狀態、DEVSEL#和TRDY#均為高電平狀態,DEVSEL#為低電平且TRDY#為高電平狀態,DEVSEL#和TRDY#均為低電平狀態;操作結束狀態(此狀態使DEVSEL#、TRDY#和STOP#維持一個周期高電平)。本系統接到復位信號后對系統進行復位,然后轉入空閑狀態,在空閑狀態中采樣總線,并根據總線的變化來決定下一個時鐘上升沿后狀態機轉入何種狀態,這些時序和程序中用到的信號都是基本且必須的,在進行開發時可以根據需要增添必要的狀態和信號,VHDL對狀態機的描述如下。

type pci_state is (Idle, Ready, DevTrdyHi, DevLoTrdyHi, DevTrdyLo, OprOver);

signal c_state :pci_state;

Idle為空閑狀態;Ready為準備狀態;DevTrdyHi表示DEVSEL#和TRDY#均為高電平狀態;DevLoTrdyHi表示DEVSEL#為低電平且TRDY#為高電平狀態;DevTrdyLo表示DEVSEL#和TRDY#均為低電平狀態;OprOverr表示操作結束狀態。

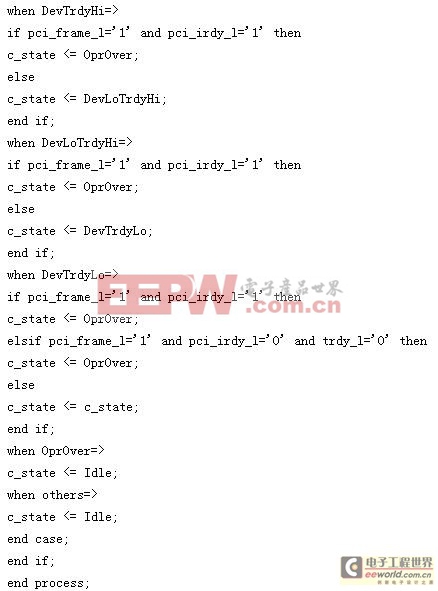

程序如下。

下一步應列出每個狀態所對應的并發事件,寫出相關的進程。進程語句是一個并行語句,它定義進程被激活時將要執行的特定行為。例如,在Ready狀態時,就要判斷從主設備方發來的地址信息是否與從設備地址相同,因此要寫出地址比較進程。

評論