基于FPGA的PCI總線接口原理研究與設計

address_compare:process(pci_rst,pci_clk),主要內容是對地址譯碼,判斷地址是否在從設備空間,如果在此空間則可做下一步動作,否則不做其他動作。

從以上分析過程可以得到整個設計思路如下:在時鐘的上升沿采樣FRAME#、地址和命令,如果FRAME#有效則譯碼地址和命令,如果總線命令為011x,并且總線上的地址在目標地址范圍內,表明這是對本設備的存儲器操作;或者總線命令為101x,且IDSEL信號有效,表明這是對本設備配置空間的操作。在這兩種情況下,根據總線命令的最后一位確定是讀操作還是寫操作,有效DEVSEL#和TRDY#信號,開始數據傳輸;并在傳輸過程中采樣FRAME#和IRDY#信號,確認最后一個數據周期,無效DEVSEL#和TRDY#信號,結束數據傳輸。

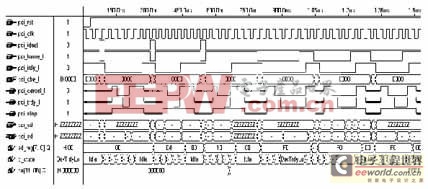

通過以上設計,在MAX+PLUSII環境下的其中一組

結束語

本文給出了在PCI總線上利用FPGA技術設計PCI總線接口的設計方案。利用這項技術可以將自己的的算法技術和一些軟件做成硬件,固化到卡上,這樣既提高了運行速度,也可以保護知識產權。

評論