FPGA與ADSP TS201的總線接口設計方案

2.1 32位數據總線,32位寄存器,寫操作

前面提過,DSP采用流水協議寫FPGA時,流水深度固定為1,FPGA在前一時鐘沿采到地址、WRx信號有效,在下一時鐘沿就鎖存數據,如圖3所示,FPGA在時鐘沿1采到地址總線上的地址與寄存器地址一致,WRx信號為低,寫標志信號S_W_FLAG置高,由于采用同步設計,FPGA只有在時鐘沿2才能采到S_W_FLAG為高,一旦采到S_W_FLAG為高,FPGA就鎖存數據總線上的數據,即在時鐘沿2鎖存數據。

2.2 32位數據總線,32位寄存器,讀操作

與寫寄存器不一樣,讀寄存器時流水深度在1到4之間可設,需要注意的是,為避免總線沖突,

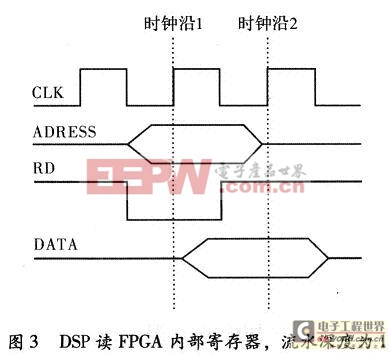

如果流水深度設置為1,FPGA在前一時鐘沿采到地址、RD信號有效,應確保在下一時鐘沿數據已經穩定的出現在數據總線上,否則DSP不能正確讀取數據,如圖3所示,在時鐘沿1采到地址總線上的地址與寄存器地址一致,RD信號為低,驅動數據總線,在時鐘沿2數據已穩定出現在數據總線上,DSP可以讀取。

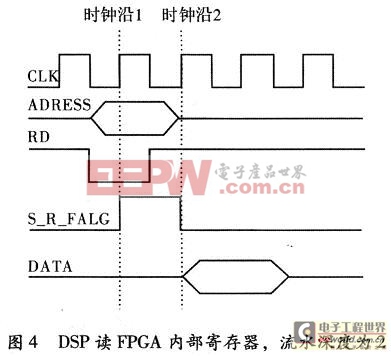

如果流水深度設置為2,FPGA在前一時鐘沿采到地址、RD信號有效,應確保隔一時鐘周期后,數據穩定的出現在數據總線上,這樣就像寫操作一樣,需要加一個標志,當條件滿足,標志為高,一旦標志為高,輸出數據,如圖4所示。

綜上所述,流水深度加深一級,FPGA就晚一個時鐘周期驅動數據總線。可以看出,雖然流水深度在1~4之間可設,但是總能保證一個時鐘周期傳輸一個數據。

評論