基于FPGA的IPV6數字包的拆裝實現

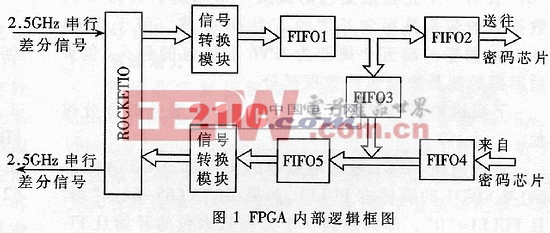

筆者在參加國家“863”重大專題項目“高速密碼芯片及驗證平臺系統”的過程中,遇到了將IPV6數據包的包頭和數據部分拆開,然后在數據部分送密碼芯片進行加/解密處理,最后再將處理后的數據部分與包頭重新封裝為數據包的課題。以往對IP包進行拆裝多利用軟件實現,但本項目涉及到配合高速密碼芯片(處理速度在2Gbit/s以上)工作的問題,顯然利用軟件實現IP包的拆裝在速度上達不到要求。為此,筆者運用FPGA(型號為Xilinx公司的XC2VP20-FF86CGB0345)來實現IPV6數據包的拆裝。該FPGA內部邏輯框圖如圖1所示。

其工作流程為:2.5GHz的標準IPV6數據包串行差分信號通過ROCKETIO高速通道后轉換為16位125MHz并行信號,再經信號轉換模塊進一步轉換為66位62.5MHz并行信號后進入FIFO1緩存,然后對其輸出數據進行判斷,若是報頭則送入FIFO3緩存,若是數據部分則送入FIFO2緩存,最后將FIFO2數據送往密碼芯片進行處理;經密碼芯片處理的數據首先放入FIFO4進行緩存,然后控制FIFO3和FIFO4將一個數據包的頭和數據寫入FIFO5中,重新封裝成一個完整的數據包;重新封裝的IPV6數據包經過信號轉換模塊變為16位125MHz的并行信號,并通過ROCKETIO高速通道轉換為2.5GHz高速串行差分信號送出。

可以看出,經過以上流程,實現了一個數據包的拆分和重新封裝。

1 IPV6數據包的拆分

用FPGAP實現IPV6數據包的拆分,主要是通過控制幾個FIFO的數據輸入輸出來實現的。FPGA內部的拆分單元電路的物理連接如圖2所示,其中FIFO的作用是緩存IPV6數據包,FIFO2的作用是緩存IPV6數據包的數據部分,FIFO3的作用是緩存IPV6數據包的包頭。

相關推薦

-

herbertwj | 2004-08-15

-

-

-

xiaohua | 2002-09-24

-

-

-

-

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

-

-

-

評論