基于FPGA的IPV6數字包的拆裝實現

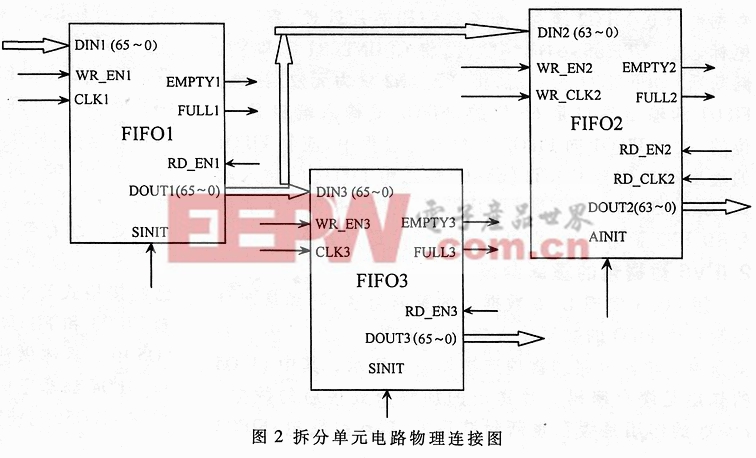

圖中的三個FIFO都是由Xilinx公司的開發工具ISE6.1自帶的Core IP生成的。其中FIFO1和FIFO3是同步FIFO,工作時鐘為頻率62.5MHz,輸入輸出數據寬度都是66bit;FIFO2是異步FIFO,輸入時鐘頻率為62.5MHz,輸出時鐘頻率為50MHz(密碼芯片的工作時鐘頻率為50MHz),輸入輸出數據寬度都是64bit。

FIFO1的輸入數據為IPV6數據包。可以看出,該數據是以并行的66bit信號傳輸的,即每一時鐘周期并行傳送66bit數據,其中每個周期的高兩位(即65位和64位)為數據包的頭尾標志,這是IPV6路由器內部根據實際處理需要加上的,“10”表示一個完整數據包的第一周期,“11”表示數據包的中間內容,“01”表示一個完整數據包的最后一個周期。因為IPV6數據包的包頭是固定長度的,為40字節(等于5×64bit),故數據的前五個周期為IPV6數據包的包頭,包頭后面跟的就是數據包的數據部分。

下面討論IPV6數據包的包頭和數據部分的拆分過程。

首先判斷FIFO1輸入端數據的頭尾標志DATA(65~64)與FIFO1的滿標志FULL1,如果DATA(65~64)=“10”且FULL1=“0”,即判斷到一個完整數據包的開始且FIFO1未滿,則使FIFO1的寫使能WR_EN1有效,寫入數據;如果DATA(65~64)=“01”,好判斷到一個完整數據包結束時,則使WR_EN1無效,這樣一個完整的數據包就緩存到了FIFO1時。

當判斷到FIFO1的空標示EMPTY1=“0”,即FIFO1非空間,令FIFO1的讀使能信號RD_EN1有效,將FIFO1中的數據讀出,直到EMPTY1=“1”,即FIFO1空為止。對讀出的數據設定一計數器COUNTER1進行計數,當DONT1不為0即FIFO1輸出端有信號時開始計數。當0COUNTER1=5時,令FIFO3的寫使能信號WR_EN3有效,將數據包的包頭寫FIFO3緩存;當COUNTER1>5時,令WR_EN3無效,WR_EN2有效,將IPV6數據包的數據部分送FIFO2緩存,準備送密碼芯片處理,直到頭尾標志DOUT1(65~64)=“01”時,將COUNTER1清零,在判斷到COUNTER1為0后,將WR_EN2置為無效。注意:FIFO1的輸出端口是66位,FIFO2的輸入端口是64位的,故在FIFO1向FIFO2寫數據的過程中,應將FIFO1的輸出端口信號DOUT(63~0)傳送給FIFO2的輸入端口DIN2(63~-)。當判斷到FIFO2非空間,將其讀使能信號RD_EN2置為有效,即可向密碼芯片送出數據。

相關推薦

-

-

-

-

xiaohua | 2002-09-24

-

sandman555 | 2005-02-05

-

-

herbertwj | 2004-08-15

-

-

-

-

-

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

評論