利用8051內核使SoC設計不再復雜的模擬仿真

在前面描述中可以看到,在該芯片設計中由于采用標準的8051核,其指令系統和體系結構基本沒有改變,但其中一些特殊寄存器與外圍模塊之間建立了映射關系,中斷源也得到了擴充。因此,驗證和仿真器的設計關鍵在于能否正確反映這些寄存器的狀態或通過寄存器控制這些外圍模塊的工作。

在系統芯片設計流程中,仿真器的設計與芯片設計同步甚至要提前,因此沒有現成的CPU芯片作仿真器核心;而簡單地將CPU與FSK、DTMF、CAS等功能芯片組合起來替代該CPU芯片,不能實現完全仿真和模擬,特別是無法獲得外圍模擬模塊的狀態。

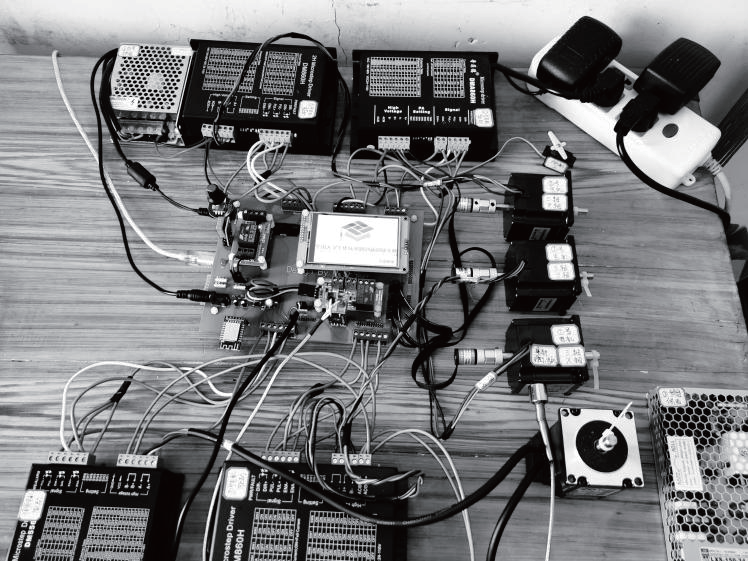

在這里,我們采用FPGA和FSK、DTMF、CAS等功能芯片組合成模擬CPU來替代所設計的系統芯片,系統結構可參照圖3。圖3中,8051核及數字接口部分由FPGA實現;CID部分中,FSK、DTMF、CAS、振鈴檢測等模塊則由相應硬件模塊實現。

圖3 短消息系統芯片仿真方案圖

FSK、DTMF、CAS、振鈴檢測等模塊通過接口與FPGA中8051相應寄存器對應,這樣在這些外圍模塊動作的同時,在8051寄存器中都能正確映射;反之FPGA中相應寄存器的改變,會引起這些外圍模塊的動作。

圖3是建立在通用8051仿真器上的短消息系統芯片仿真方案。模擬CPU模塊集成了FPGA和CID部分芯片和電路,該模塊采用與8051定義一致的引腳與仿真板相連。對于仿真板來說,該模塊的命令和操作與標準8051是一致的,因此通用的仿真和集成環境不需要改變。仿真接口由通用8051仿真接口和模擬CPU模塊中的CID外接信號共同組成,其引腳封裝定義與系統芯片一致。這樣通過通用仿真集成環境可以觀察和控制CID部分電路,從而實現了對整個短信息系統芯片的完全驗證和仿真。

采用該方法,具有以下優點:

◇ 實現了對該SoC芯片系統功能的驗證;

◇ 完全兼容現有集成開發和仿真環境;

◇ 簡化了數模混合設計的驗證問題;

◇ 經過改進,可以利用通用仿真器仿真和調試硬件、軟件;

◇ 由于FPGA可以隨著芯片的改進而重新編程,因此增大了設計和驗證的靈活性;

◇ 縮短了開發時間,加快芯片上市時間。

4 結論

利用該方案構成的系統芯片驗證和仿真方案已經在我們的設計中得到了應用。事實上,利用該方案的思想不僅可以實現基于8051核系統芯片的驗證和仿真,其它系統芯片的驗證和仿真也是可以借鑒的。

評論