通過FLIX指令結構提高可配置處理器計算性能

指令集的性能更多地是與有用的操作個數相關,而不是與每個執行部件的執行時間或者每個時鐘的執行相關。然而,高性能并不能保證系統具有良好的靈活性。指令集的靈活性與不同應用領域的多樣性相關,在這些應用中,數據運算能夠在指令流中進行有效編碼。一個較長的指令字一般可以允許更多數量和更多樣性的操作以及操作數標志符在每個指令字中進行編碼。

在RISC體系結構中,一條指令通常只對一個原始操作進行編碼。在長指令字體系結構中,一條指令可以允許對多個獨立的子指令進行編碼,每條子指令都有自己的操作和操作數標志符。每條子指令可以是一般的類似于RISC指令的操作或者是一條比較復雜的專用操作。指令字設計的越長,那么對于任意給定的操作數個數和操作個數而言,指令編碼就越簡單,正交性就越好。

長指令字處理器速度并不總是比RISC處理器快。有時,RISC處理器執行單元的簡單性所帶來的優點將使得處理器能夠以最大時鐘頻率運行,并且每個時鐘周期可以執行幾條獨特的RISC指令,這將能夠彌補因RISC指令集相對簡單所帶來的損失。盡管如此,在絕大多數要求數據密集型的任務中使用RISC指令集,但是指令集采用超標量方式實現,每個時鐘周期執行多條指令,這同長指令字體系結構中那種充分利用程序代碼中潛在的指令操作的并行性是一樣的。

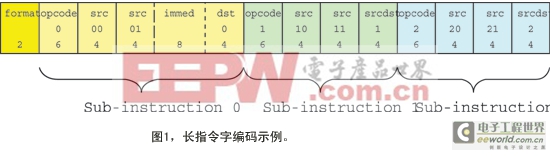

圖1表示一個基本的長指令操作編碼示例,圖中列出一個64位的指令字,該指令字包括三個獨立的子指令槽,每個指令槽說明一個操作和若干操作數。第一個子指令(子指令0)有一個操作碼和四個操作數說明符(包括兩個源寄存器、一個立即數域和一個目的寄存器)。第二個和第三個子指令(子指令1和2)各有一個操作碼和三個操作數說明符(兩個源寄存器和一個源/目的寄存器)。左邊的兩位格式域表示各個子指令的特定分組情況。如果處理器支持變長指令編碼的話,那么兩位的格式域也可以表示整個指令的長度。

顯然,系統硬件開銷和長指令字是相關的。指令存儲器位數越寬,譯碼邏輯就越大,并且系統就需要更多數量的執行部件,而且寄存器文件(或者寄存器文件端口)實現就必須滿足指令并行性的要求。更大的硬件邏輯模塊越多,系統優化就越困難,所以,同相對簡單和位數較少的RISC指令那樣編碼相比較,整個系統的最大時鐘頻率就會降低。盡管如此,追求系統性能和靈活性的優點還是最基本的,尤其是對于那些具有高的程序潛在并行性的數據密集型應用。

在有些長指令字體系結構中,每個子指令都幾乎具有完整的獨自資源,包括專用執行部件、專用寄存器堆和專用的數據存儲器。在另外一些處理器體系結構中,所有子指令共享公用寄存器堆和數據存儲器,為保證有效的數據共享系統需要大量的數據端口與公用存儲器結構.

長指令字體系結構對于如下問題而言也會有很大不同:一條長指令字該多“長”?對于高端計算機系統處理器(例如英特爾的安騰處理器系列)和高端嵌入式處理器(例如TI公司的TMS320C6400 DSP系列)而言,指令字確實是非常“長”,通常幾百位。對于更多的對成本和功耗敏感的嵌入式應用,指令字可能是64位。但是,一旦多個獨立的子指令打包成每個指令字后,關鍵的處理器體系結構原理都是一樣的。

代碼大小和長指令字

同每條指令只對一個獨立操作進行編碼的體系結構相比,長指令字體系結構的一個共同問題是代碼量大。這是超常指令字VLIW體系結構的一個通病,然而這對于那些片上系統(SoC)設計而言尤其重要,因為SoC系統中的指令存儲器通常會占用絕大多數的芯片面積。同那些編譯代碼有效的體系結構相比,VLIW代碼通常需要多占用代碼存儲容量的兩倍到五倍。

VLIW體系結構中程序代碼的膨脹問題部分源于指令長度的不靈活性。例如,如果編譯器只能找到一個獨立操作,其源操作數和執行部件都已經準備好,那么此時編譯器就不得不在編碼時插入空操作NOP來填滿剩下的幾個子指令操作域。指令存儲已經占用了大部分的嵌入式片上系統SoC硅片面積,因此代碼擴充就造成了更大的硬件開銷和更低的指令高速緩存性能,或者二者兼而有之。

VLIW代碼膨脹問題的第二個根源在于體系結構對常用操作的松散編碼,這在VLIW微處理器中是常見的。

然而,長指令并非必然會導致VLIW代碼膨脹問題。Tensilica的Vectra LX DSP體系結構中的一個長指令字在指令流中只需要20位就可以說明8個按照單指令流多數據流SIMD方式執行的16位乘加操作MAC,這不包括其它的加載、存儲、分支和地址計算指令。

評論