多DSP系統實現雷達極化信號兩對IQ的采集和處理

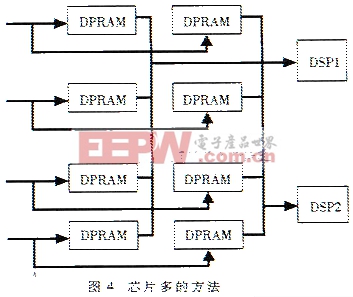

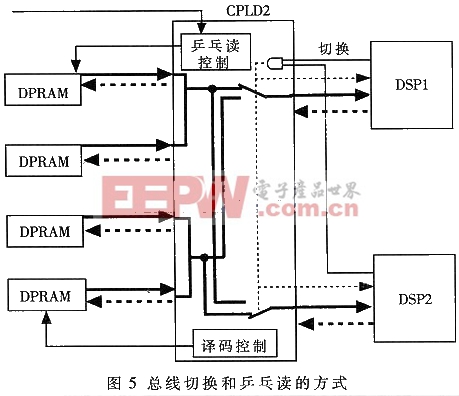

1.8 PCI接口 PCI接口采用PLX9054實現。采用C模式。顯控計算機讀寫FIFO和DPRAM,實現傳達工作模式控制極化參數讀取以及極化處理后數據讀取的任務。 1.9 SDC方位單元 該單元接收雷達自整角機送來的400Hz方位信號,通過SDC模塊轉換成數字量。CPLD對SDC模塊做邏輯控制和方位數字量的緩存。方位信息一路送到PCI接口給顯示計算機;一路送到DSP2單元,判斷方式是否進入預定的工作窗口。 1.10 邏輯控制 板上所有邏輯均由CPLD或者FPGA控制。靈活方便,易于修改。 2 幾個難點問題的設計 2.1 總線開關實現多DSP共享數據 圖4方法用的芯片多,對板上的譯碼控制、印制板走線都帶來困難。設計采用了總線切換和乒乓讀的方式見圖5,用一片CPLD實現兩個DSP對一組數據的分享。

1.8 PCI接口 PCI接口采用PLX9054實現。采用C模式。顯控計算機讀寫FIFO和DPRAM,實現傳達工作模式控制極化參數讀取以及極化處理后數據讀取的任務。 1.9 SDC方位單元 該單元接收雷達自整角機送來的400Hz方位信號,通過SDC模塊轉換成數字量。CPLD對SDC模塊做邏輯控制和方位數字量的緩存。方位信息一路送到PCI接口給顯示計算機;一路送到DSP2單元,判斷方式是否進入預定的工作窗口。 1.10 邏輯控制 板上所有邏輯均由CPLD或者FPGA控制。靈活方便,易于修改。 2 幾個難點問題的設計 2.1 總線開關實現多DSP共享數據 圖4方法用的芯片多,對板上的譯碼控制、印制板走線都帶來困難。設計采用了總線切換和乒乓讀的方式見圖5,用一片CPLD實現兩個DSP對一組數據的分享。 方法是DSP1先讀上面兩片DPRAM,與此同時,DSP2讀下面兩片DPRAM。也就是DSP1數據總線掛在上面兩片DPRAM上,DSP2數據總線掛在下面兩片DPRAM上。當DSP1讀完后發信號SW_EN1置1申請交換。同樣,DSP2讀完后也發SW_EN2置1申請交換。如果SW_EN1和SW_EN2均為1,即可以交換,DSP1上數據線掛在下兩片DPRAM,而DSP2數據線掛在上兩片DPRAM上。實現兩個DSP共享交叉讀一組雙口RAM數據。注意:切換發生后,產生一個信號SW_BUS,兩個DSP各自采樣到這個信號,表示可以讀另外兩片DPRAM的數據了。從時序圖6上可以看到,總線切換后,有20ns左右的不穩定期。所以在收到SW_BUS信號為1時,DSP要延時20ns再讀另外的兩片DPRAM。也就是DSP讀操作前加兩個NOP指令。 2.2 多DSP時序配合 系統上有4片DSP,各DSP均以雷達重復脈沖為工作節拍產生中斷,各分系統任務在一個雷達中斷完成。每個DSP處理數據的流程都是:讀數、處理、輸出。當DSP用到前面DSP處理后的數時,要比前面的DSP工作節拍慢一個中斷周期。如圖7,DSP1處理第n周期時,DSP3在處理第n-1周期的數。DSP3接收DSP1處理后的放在FIFO中的數據,DSP3處理的數據和DSP1處理的數據時間上相差一個中斷時間,也就是一個雷達脈沖周期。圖62.3 PCI接口訪問存儲器設計 設計采用基于PLX9054的數據采集方案;采用9054 C模式、PCI局部端掛存儲器的方法。PCI總線通過9054讀取采集卡中存于FIFO的DPRAM中的數據。設計工作非常簡單。用戶所做的工作為三個: 一是燒與串行EEPROM值。設置自己對系統的有關資源分配、中斷等信息的要求。 二是對PCI局部總線的地址并結合相關控制線進行譯碼,選通相應的存儲器。圖7三是利用windriver提供的驅動程序,在系統上編寫讀寫PCI設備的應用程序。 這樣,就很方便地實現了PCI設備的數據采集。

方法是DSP1先讀上面兩片DPRAM,與此同時,DSP2讀下面兩片DPRAM。也就是DSP1數據總線掛在上面兩片DPRAM上,DSP2數據總線掛在下面兩片DPRAM上。當DSP1讀完后發信號SW_EN1置1申請交換。同樣,DSP2讀完后也發SW_EN2置1申請交換。如果SW_EN1和SW_EN2均為1,即可以交換,DSP1上數據線掛在下兩片DPRAM,而DSP2數據線掛在上兩片DPRAM上。實現兩個DSP共享交叉讀一組雙口RAM數據。注意:切換發生后,產生一個信號SW_BUS,兩個DSP各自采樣到這個信號,表示可以讀另外兩片DPRAM的數據了。從時序圖6上可以看到,總線切換后,有20ns左右的不穩定期。所以在收到SW_BUS信號為1時,DSP要延時20ns再讀另外的兩片DPRAM。也就是DSP讀操作前加兩個NOP指令。 2.2 多DSP時序配合 系統上有4片DSP,各DSP均以雷達重復脈沖為工作節拍產生中斷,各分系統任務在一個雷達中斷完成。每個DSP處理數據的流程都是:讀數、處理、輸出。當DSP用到前面DSP處理后的數時,要比前面的DSP工作節拍慢一個中斷周期。如圖7,DSP1處理第n周期時,DSP3在處理第n-1周期的數。DSP3接收DSP1處理后的放在FIFO中的數據,DSP3處理的數據和DSP1處理的數據時間上相差一個中斷時間,也就是一個雷達脈沖周期。圖62.3 PCI接口訪問存儲器設計 設計采用基于PLX9054的數據采集方案;采用9054 C模式、PCI局部端掛存儲器的方法。PCI總線通過9054讀取采集卡中存于FIFO的DPRAM中的數據。設計工作非常簡單。用戶所做的工作為三個: 一是燒與串行EEPROM值。設置自己對系統的有關資源分配、中斷等信息的要求。 二是對PCI局部總線的地址并結合相關控制線進行譯碼,選通相應的存儲器。圖7三是利用windriver提供的驅動程序,在系統上編寫讀寫PCI設備的應用程序。 這樣,就很方便地實現了PCI設備的數據采集。

評論