基于TI最新多核DSP SoC架構解析

基礎局端設備OEM廠商關注的焦點正在轉變,對解決方案的功耗要求越來越高、要求可擴展的異構網絡、對MIMO功能的需求以提升接受信號接受能力。對頻譜效率的要求使得低時延、密集計算型處理環境越來越重要。

本文引用地址:http://cqxgywz.com/article/257442.htmTI多核及媒體基礎架構DSP業務部全球業務經理Ramesh Kumar表示,TI的多核SoC產品正是針對市場對上述能力的不斷需求而推出的。TI了解市場正在變化,因此推出了這一多核SoC結構,期待能為設備供應商提供更快、更便利的解決方案。

TI 最近為這一系列推出了C6x新型多核 SoC 架構,運行頻率高達1.2GHz、性能高達256GMACS/128GFLOPS,領先TI現有產品高達10倍以上的效率,領先市面上最先進產品5倍以上效率。目前這一架構已經推出了4核和8核系列產品,針對無線基站解決方案(包括macro/pico/femto基站)和媒體網關/網絡應用。

C6x新型多核SoC架構

新的多核DSP基于40nm工藝,受益于先進的節點,新的產品將在性能、集成度、功耗上有大幅提升。除了時鐘頻率外,最具特點的就是集成了定點和浮點處理功能。DSP都有定點計算的功能,增加了浮點計算后,在無線基站和視頻方面有很大提升。使用定點DSP,他們開發浮點算法,檢測滿意后,再轉化成定點算法。使用這系列多核SoC,工程師不需要通過浮點轉定點,可以直接進行處理,這通常也能節省3個月以上的時間。

另外,WiMAX、LTE的標準還在不斷演進中,可編程DSP環境,工程師可以很快增加新的編解碼器,通過軟件隨時更新。

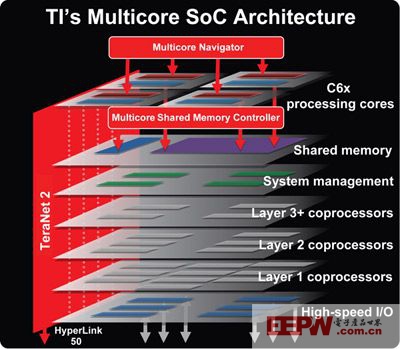

多核處理器的效能要得到發揮,對各個內核的管理和協調至關重要。如果內核無法高效互聯,性能也會打折。TI花了很多精力在核間的互聯上,保證高效的處理能力。 TI的SoC通過多核導航器實現內核的高效管理,它充分利用了8192任務型隊列優化數據流的片上網絡管理單元,采用基于主機/緩沖器描述模型使用的數據包/消息。 TeraNet 2 能夠互聯內核的協處理器和外設,速度達每秒2兆兆位的無阻塞主干網。除了每個內核的片上內存外,SoC還有共享的內存部分,通過共享內存控制器,無需橫越TeraNet 2就可以直接訪問內核。

全新的架構配合TI 多核開發工具,高效率的編譯器加上最優的調試分析工具讓代碼更快地應用于現場,Jump Start軟件還提供了GSM-EDGE、WCDMA-HSPA+、WiMAX以及LTE軟件庫,對3G和4G的支持也相當完善。

評論