基于C64x+ DSP高速緩存一致性分析與維護

硬件維護的CACHE一致性

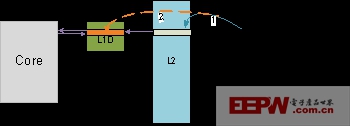

在C64x+平臺上,硬件會對5)的情況自動進行數據一致性維護。分析需要分為讀寫兩類操作進行,圖 5和圖 6分別描述了內核對L2上的數據進行讀和寫的情況。

圖 5 內核讀L2數據的情況

圖 6 內核寫L2數據的情況

其它主機要對L2中的內容進行更新操作時,L2控制器會根據被更新數據的地址判斷相應的地址是否在L1D CACHE中,如果在L1D CACHE中,硬件會自動將更新的數據拷貝一份到L1D CACHE中。如果要讀取的數據不在L1D CACHE中,L1D控制器會自動從L2加載數據,內核也可以得到更新后的數據。過程如圖 5中的1和2所示,這樣就可以解決一致性的問題。

其它主機要對L2中的內容進行讀操作的時候,L2控制器會判斷要讀取的數據地址是否在L1D CACHE中,對于在L1D CACHE中的數據,硬件會自動從L1D CACHE中讀取最新的數據。對于不在L1D CACHE中的數據,說明L2中的數據已經是最新的數據,可以直接從L2中讀取。通過這樣的處理,可以保證其它主機讀到內核更新后的數據,從而可以解決一致性的問題。過程如圖 6中的1和2所示。

軟件維護的CACHE一致性

在C64x+平臺上,2)、3) 和6)的情況需要軟件進行的一致性維護操作以保證內核或者其它主機可以得到最新的數據。

C64x+ 軟件一致性維護實現

C64x+平臺上由軟件控制的一致性維護操作包含三種:CACHE數據失效、CACHE數據回寫和CACHE數據回寫并失效。啟動維護操作需要配置相應的基地址和計數寄存器,當計數寄存器中的值變為0時表示操作完成。TI提供的芯片支持庫中也提供了相應的API來完成相應的功能。各種操作涉及的各級CACHE的一致性操作控制寄存器列在表2中。

表 2 C64x+ CACHE一致性維護寄存器

評論