基于C64x+ DSP高速緩存一致性分析與維護(hù)

數(shù)據(jù)CACHE一致性

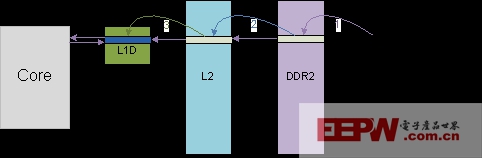

對(duì)于數(shù)據(jù)部分的一致性維護(hù),需要由軟件維護(hù)的情況是6),包括內(nèi)核對(duì)DDR2的讀取和寫兩種情況。圖 9和圖 10分別描述了這兩種情況。

圖 9 內(nèi)核對(duì)DDR2上的數(shù)據(jù)讀的情況

圖 10 內(nèi)核對(duì)DDR2上的數(shù)據(jù)寫的情況

本文小結(jié)

高速緩存一致性問(wèn)題是DSP應(yīng)用中常見的問(wèn)題,TI C64x+ DSP是業(yè)界高性能信號(hào)處理平臺(tái),具有優(yōu)良的高速緩存性能。C64x+平臺(tái)上高速緩存一致性問(wèn)題維護(hù)可以歸納為以下兩點(diǎn):1) 代碼部分的一致性問(wèn)題需要由軟件來(lái)維護(hù);2) 只有當(dāng)內(nèi)核和其它主機(jī)共同需要訪問(wèn)的數(shù)據(jù)緩沖區(qū)在外部存儲(chǔ)器中的時(shí)候,數(shù)據(jù)高速緩存一致性問(wèn)題才需要由軟件來(lái)進(jìn)行維護(hù)。其它情況下,數(shù)據(jù)高速緩存一致性都會(huì)由硬件自動(dòng)完成。

評(píng)論