如何在FPGA中實現狀態機

FPGA常常用于執行基于序列和控制的行動,比如實現一個簡單的通信協議。對于設計人員來說,滿足這些行動和序列要求的最佳方法則是使用狀態機。狀 態機是在數量有限的狀態之間進行轉換的邏輯結構。一個狀態機在某個特定的時間點只處于一種狀態。但在一系列觸發器的觸發下,將在不同狀態間進行轉換。

本文引用地址:http://cqxgywz.com/article/266770.htm理論上講,狀態機可以分為Moore狀態機和Mealy狀態機兩大類。它們之間的差異僅在于如何生成狀態機的輸出。Moore狀態機的輸出僅為當前 狀態的函數。典型的例子就是計數器。而Mealy狀態機的輸出是當前狀態和輸入的函數。典型的例子就是Richards控制器。

定義狀態機

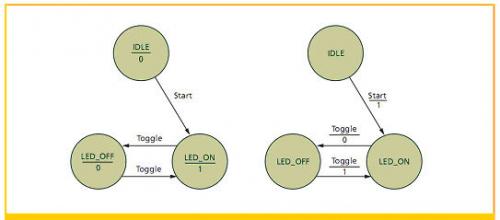

當需要定義一個狀態機時,首先要繪制一張狀態圖。狀態圖可用來顯示狀態、狀態間的轉換和狀態機的輸出。圖1顯示了Moore狀態機的狀態圖(左)和Mealy狀態機的狀態圖(右)。

圖1,用于開/關LED的Moore狀態機(左)和Mealy狀態機(右)的狀態圖。

如果您要在物理組件中實現這些狀態圖(工程師在FPGA問世之前就是這么做的),首先就得生成當前狀態和后續狀態表,然后生成實現狀態機所需的邏輯。不過由于我們將使用FPGA來實現設計,因此我們可以直接從狀態轉換圖開始工作。

算法狀態圖

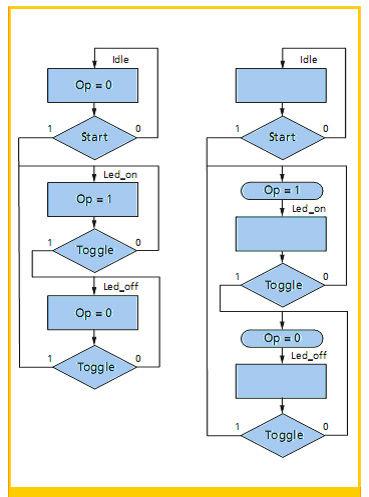

雖然有許多狀態機是使用圖1所示的狀態圖方法進行設計的,但另外還有一種描述狀態機行為的方法,這就是算法狀態圖法。ASM圖(圖2)在外觀上更加接近軟件工程流程圖。它由三個基本部分構成:

狀態框。它與狀態名稱有關,并包含Moore狀態輸出列表。

決策框。如果檢驗某條件為真,則進行下一狀態的判斷。

條件輸出框。讓狀態機根據當前狀態和輸入描述Mealy輸出。

一些工程師認為,如果使用VHDL等硬件描述語言,則采用ASM格式進行描述的狀態機更易于映射到實現方案中。

圖2,用于圖1所示的狀態機(Moore狀態機(左),Mealy狀態機(右))的算法狀態圖。

Moore和Mealy:應該選擇哪個?

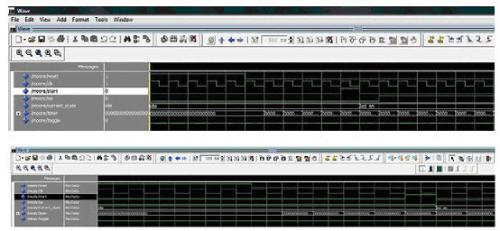

實現Moore狀態機還是Mealy狀態機,取決于狀態機需要實現的功能,以及特定的反應次數要求。兩種狀態機之間的最大差別在于狀態機如何對輸入 做出反應。在輸入和設置的適當輸出之間,Moore狀態機一般有一個時鐘周期的延遲。這就意味著Moore狀態機無法對輸入變化立即做出反應,這點在圖3 中可以清楚地看到。而Mealy狀態機則能夠立即對輸入做出反應,這通常意味著:實現相同的函數,Mealy狀態機比Moore狀態機需要更少的狀態。 Mealy狀態機的不足之處就是在與另一個狀態機進行通信時,如果輸出出乎意料地嚴重依賴于其它事件的序列或時序,就可能會發生紊亂情況。

圖3,截屏顯示了Moore狀態機(上)和Mealy狀態機(下)輸出的仿真結果。

當然,并非只能使用單純的Moore狀態機或Mealy狀態機,也可以將這兩種狀態機混合使用,從而更有效地實現所需的函數。比如說,用于接收RS232串行數據的狀態機就可以是混合機。

fpga相關文章:fpga是什么

塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論