FPGA設計開發軟件ISE使用技巧之:典型實例-ChipScope功能演示

(18)開始采樣調試。

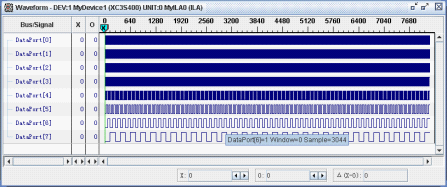

本文引用地址:http://cqxgywz.com/article/269339.htm 單擊左上角的![]() 運行按扭,開始采樣。捕獲觸發條件后,ChipScope將采集所設置存儲深度的波形,如圖6.74所示。

運行按扭,開始采樣。捕獲觸發條件后,ChipScope將采集所設置存儲深度的波形,如圖6.74所示。

圖6.74 采集信號的波形圖

在波形顯示窗口下可對波形進行放大

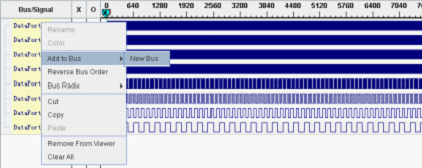

圖6.75 組合總線數據

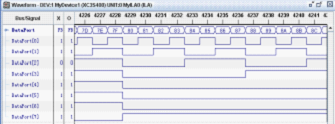

添加成功后,就可以在新生成的Bus下看到總線數據,如圖6.76所示。圖中DataPort為新生成的總線,設計者可以根據需要修改總線的名稱。

圖6.76 總線數據生成結果

通過上述步驟就完成了應用ChipScope Pro的一個完整的流程,這種流程是通過修改源代碼來添加邏輯分析儀的。下面的流程可以不用修改設計代碼,直接將邏輯分析儀插入到設計的網表文件中,使用方便,應用比較廣泛。

6.8.3 基于ChipScope Pro Core Inserter的實現流程

基于ChipScope Pro Core Inserter實現流程的具體步驟如下。

(1)新建工程,添加源代碼。

參見第一種實現流程的同一步驟。

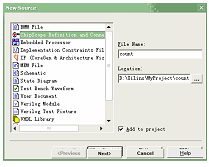

(2)新建ChipScope Pro 資源。

選擇ISE的“Project”/“New Source”,再選擇“ChipScope Definition and Connection”選項,輸入新建資源的名稱:count,生成count.cdc資源文件。如果有現成的擴展名為cdc的文件,也可以通過“Project”/“Add Source”來添加,如圖6.77所示。

完成后在工程瀏覽器中可以看到包含的count.cdc文件,如圖6.78所示。

圖6.77 新建.cdc資源對話框 圖6.78 新建.cdc資源結果

(3)綜合。

與前一種設計流程不同,這里要先對源文件進行綜合,在這種設計流程中,ILA核是直接插入到設計綜合后生成的邏輯網表中的,因此要先對源文件進行綜合。

(4)設置ICON及ILA各項參數。

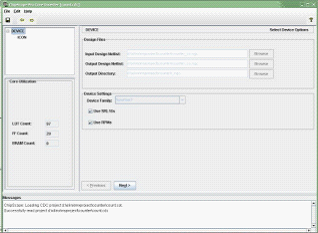

在工程瀏覽器中雙擊count.cdc文件,打開ChipScope Pro Core Inserter工具,如圖6.79所示。

圖6.79 ChipScope Pro Core Inserter用戶界面

在圖中可以看到,這里無需再設置輸入網表文件的路徑,系統會自動找到網表文件,并設置輸出文件的路徑。

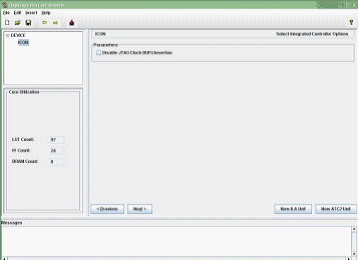

單擊“Next”按鈕進入ICON核設置頁面,如圖6.80所示。

圖6.80 “Select Integrated Controller Options”ICON對話框

其中,“Disable JTAG Clock BUFG Insertion”用于指定是否禁止在JTAG時鐘上插入BUFG。如果選中此項,JTAG時鐘將使用普通布線資源,而不是全局時鐘布線。這里此項不選,用全局時鐘布線。

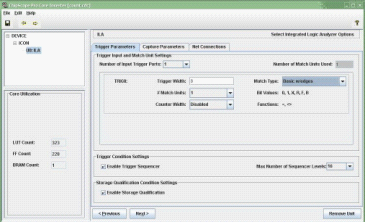

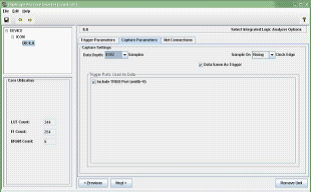

完成ICON核的設置以后,選擇單擊“Next”按鈕,進入ILA核設置頁面,如圖6.81所示。

圖6.81 “Trigger Parameters”選項卡設置

在觸發器設置頁面中,設置觸發端口數、觸發寬度、觸發條件單元函數和個數等。如有不一致,請讀者對照上圖修改,設置完畢后單擊“Next”按鈕出現如圖6.82所示對話框。

圖6.82 “Capture Parameters”選項卡設置

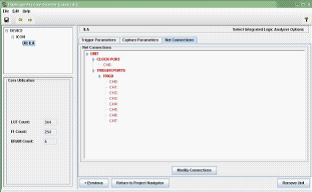

如圖6.82所示,設置存儲深度為8192,采樣時刻為上升沿。選中“Data Same As Trigger”,即數據信號與觸發信號相同。設置完畢后單擊“Next”按鈕,可以看到已經定義的ILA,如圖6.83所示。

圖6.83 “Net Connection”選項卡設置

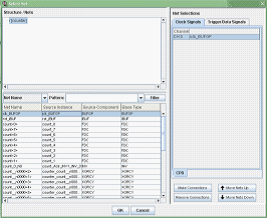

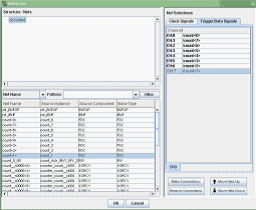

此時由于還沒有對網表進行映射,因此網絡線都是呈紅色顯示。單擊“Modify Connection”按鈕,設置時鐘信號和TRIG信號與要觀測的信號的映射關系,如圖6.84及6.85所示。

圖6.84 設置時鐘信號連接

圖6.85 設置數據連接

fpga相關文章:fpga是什么

塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論