最小化ARM Cortex-M CPU功耗的方法與技巧

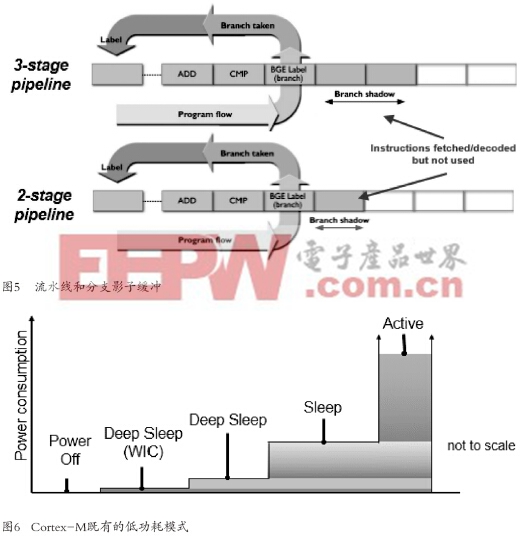

此外,Cortex-M0+內核也可以通過減少到兩級流水線而降低功耗。在通常的流水線處理器中,下一條指令在CPU執行當前指令時被取出。如果程序產生分支,并且不能使用下一條取出的指令,那么被用于取指(分支影子緩沖器)的功耗就被浪費了。在兩級流水線中,這個分支影子緩沖器縮小了,因此能耗得以節省(雖然僅有少量),這也意味著在發生流水線刷新時,僅需要不到一個時鐘周期就能重新填充流水線(如圖5所示)。

5 利用GPIO端口節能

Cortex-M0+內核提供節能特性的另一個地方是它的高速GPIO端口。在Cortex-M3和Cortex-M4內核中,反轉一位或GPIO端口的過程是“讀-修改-寫”一個32位寄存器。雖然Cortex-M0+也可以使用這個方法,但是它有一個專用的32位寬I/O端口,可以采用單時鐘周期訪問GPIO,使得它能夠高效的反位/引腳反轉。注意:在Cortex-M0+上,這是一個可選的特性,并不是所有供應商都具備了這個有用的GPIO特性。

6 CPU的休眠模式

減少CPU功耗的最有效方法之一是關閉CPU自身。在Cortex-M架構中有多種不同的休眠模式,每一種都在功耗和再次執行代碼的啟動時間之間進行了折中考慮(如圖6所示)。它也能夠讓CPU在完成中斷服務后自動進入某個休眠模式,而不需要執行任何代碼去完成這個工作。這種方法可以為那些常見于超低功耗應用中的任務節省CPU時鐘周期。

在深度睡眠模式下,也可以使用喚醒中斷控制器(WIC)來減輕NVIC負擔。在使用WIC時,為實現低功耗模式下外部中斷喚醒CPU,無需為NVIC提供時鐘。

7 自主型外設可減輕CPU負荷

自主型片上外設具有降低功耗的優點。大多數MCU供應商已經在本身產品架構中實現了外設之間的自主型交互,例如Silicon Labs的EFM32 MCU使用的外設反射系統(PRS)。自主型外設能夠實現十分復雜的外設動作鏈(觸發而不是資料傳輸),同時保持CPU處于休眠狀態。例如使用EFM32 MCU上的PRS功能,應用能夠被配置為在CPU休眠的低功耗模式下,當片上比較器檢測電壓值超過了其預設的門限值,則觸發一個定時器去開始減數。當定時器到達0時,觸發DAC去開始輸出 — 所有事件發生過程中CPU可以一直保持休眠狀態。

自動進行如此復雜的交互,這使得外設之間能夠完成大量工作而無需CPU參與。此外,帶有內建智能的外設(例如傳感器接口或脈沖計數器)能夠通過預設的條件用于中斷喚醒CPU,例如在累積10個脈沖時中斷喚醒CPU。在這個例子中,當CPU被特定中斷喚醒時,它明確知道需要做什么,而不需要檢查計數器或寄存器以判別發生了什么,因此可以節省相當多的時鐘周期,更好的完成其他重要任務。

我們已經介紹了多種易于實現的減輕Cortex-M設備上CPU功耗的方法。當然,還有其他因素影響功耗,例如用于加工設備的處理工藝或者用于存儲應用代碼的存儲器技術。工藝和存儲技術能夠顯著影響運行時功耗和低功耗模式下的漏電,因此也應當納入嵌入式開發人員的整體功耗設計考慮之中。

存儲器相關文章:存儲器原理

評論