基于Modelsim FLI接口的FPGA仿真技術

3、C語言對 VHDL設計的協同仿真

本文引用地址:http://cqxgywz.com/article/273718.htm3.1 構成框圖

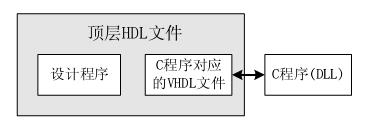

仿真文件的構成如圖 3 所示,包括 HDL 文件和動態鏈接庫(即 C 程序)。圖中 C 程序對應的 VHDL 文件要負責聲明對應的動態連接庫文件名及初始化函數,另外還可以給出一些調用參數。動態鏈接庫中用到的輸入輸出信號也要在對應的 VHDL 文件中聲明。

圖3 仿真文件構成示意圖

例如,假定有一個DLL文件名為sim.dll,對應的初始化函數為sim_init,有輸入信號in1,in2,輸出信號 out1,out2,可以這樣編寫對應的 VHDL 文件 (sim.vhd):

library ieee;

use ieee.std_logic_1164.all;

entity sim is

port(

in1: in std_logic;

in2: in std_logic;

out1: out std_logic;

out2: out std_logic;

);

end entity sim;

architecture dll of sim is

attribute foreign : string;

attribute foreign of dll : architecture is "sim_init sim.dll”

begin

end;

仿真時,仿真器對頂層的 HDL 文件進行仿真,并根據各 VHDL 文件的動態鏈接庫聲明來調用、執行相應的動態鏈接庫。

3.2 動態鏈接庫的程序結構

modelsim 在仿真時,根據 VHDL 文件的聲明,調用 DLL 文件(如 sim.dll)。在 VHDL文件中已經給出了調用文件(sim.dll)和初始化函數名(如 sim_init),modelsim根據這些信息,調用 sim.dll中的 sim_init 函數,完成初始化工作。初始化包括:

1. 初始化全局變量;

2. 設置 VHDL 輸入輸出信號與 C 程序變量的對應關系;

3. 設置輸出信號的一些初始狀態(mti_ScheduleDriver);

4. 設置在仿真器重新仿真(restart)和仿真器退出仿真(quit)等情況下執行的一些函

數(mti_AddRestartCB 和mti_AddQuitCB 等),如釋放動態申請的內存等等;

5. 設置敏感表,給出在某些信號發生某些變化(如時鐘上升沿等)時執行的函數。

6. 等等。

下面結合 3.1的例子(sim.vhd),給出C 程序的設計步驟。

1.包含頭文件,包括 C程序常用的一些頭文件和 Modelsim給出的外部語言接口頭文件m ti.h。Modelsim給出的外部接口函數說明、類型定義等都在 mti.h 中。

2.定義自己的結構體,這一點主要是為了編程方便,例如輸入輸出信號對應的變量在各函數中基本上都會用到,可以把這些變量定義成一個結構,便于參數傳遞。例如,我們可以把 3.1 的 sim.vhd 輸入輸出信號對應的變量定義成結構:

typedef struct {

driverID out1;

driverID out2;

signalID in1;

signalID in2;

}PortStruct;

其中 driverID 表示輸出信號對應的變量;signalID表示輸入信號對應的變量。這樣,這里定義的變量 out1, out2, in1, in2 就分別與 sim.vhd中的信號 out1, out2, in1, in2 對應。

fpga相關文章:fpga是什么

評論