LPCVD TEOS 厚度的機械應力對閃存循環性能的影響

摘要:本文研究了閃存循環(耐久性)與LPCVD(低壓化學氣相沉積)制程應變的相關性。所沉積的充當S/D植入物犧牲氧化層的12.5nm SCTEOS在后面的工序中會被去除。然而有趣的是,通過應力記憶技術(SMT),我們發現對通道產生的應力會影響閃存循環(耐久性)性能

【關鍵詞:耐久性/循環、LPCVD TEOS、應力】

引言

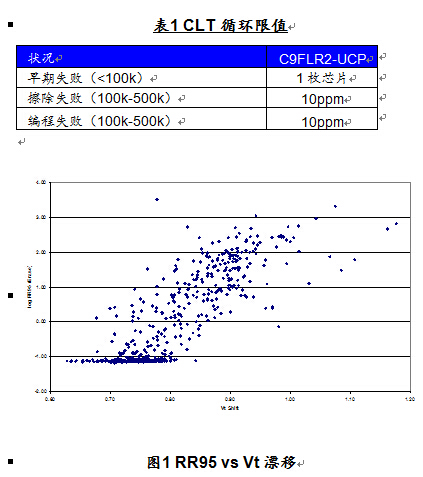

2008年2月,有報道稱,嵌入式閃存UCP遇到擦除原始比特失敗率(RR)高于CLT(置信度檢測)S5循環中10ppm的限值(查閱表1獲取CLT限值)問題。這會造成晶圓報廢,也不利于平穩提升產量。為了探尋問題的根本原因、以及有助于獲取更多裕度的最佳工藝條件,相關人員開展了許多研究和評估。循環原始比特失敗率的另一種響應是Vt(閾值電壓)漂移(Vt EOL - Vt BOL),我們發現RR(對數)和Vt之間存在密切的關系——如圖1所示。

本文研究了LPCVD TEOS薄膜應力對閃存循環的影響,目的是以較少的Vt漂移獲得更多循環制程裕度。SiN(HTN)薄膜引起的機械應力會影響閃存循環性能是眾所周知的事實,這個現象已經得到了廣泛的研究。但針對LPCVD TEOS薄膜應力的研究幾乎沒有。因此,本文將借助實驗結果進一步探討LPCVD薄膜的影響。

三個DOE批次的LPCVD TEOS薄膜厚度清楚地表明,循環Vt漂移與TEOS薄膜厚度之間有密切的聯系。我們發現循環Vt漂移與LPCVD TEOS薄膜厚度之間的關系與薄膜的機械應力有關。這一點可以用制程應變也就是所謂的應力記憶技術(SMT)解釋。退火時應力會從TEOS薄膜轉移到通道上[1]。因為與基片表面平行的壓縮應力,存儲單元中的編程/擦除(P/E)循環會產生更多界面陷阱,從而導致Vt漂移增大。而將LPCVD TEOS薄膜厚度從12.5nm降至11.5nm,可以獲得額外的約20mV Vt漂移的循環制程裕度。

實驗方法

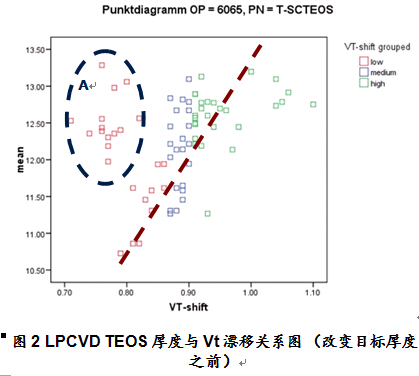

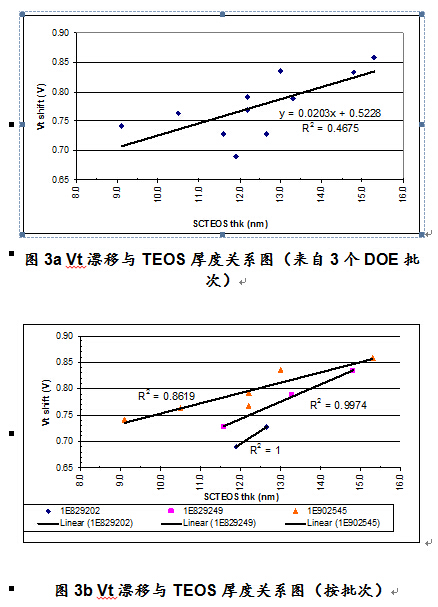

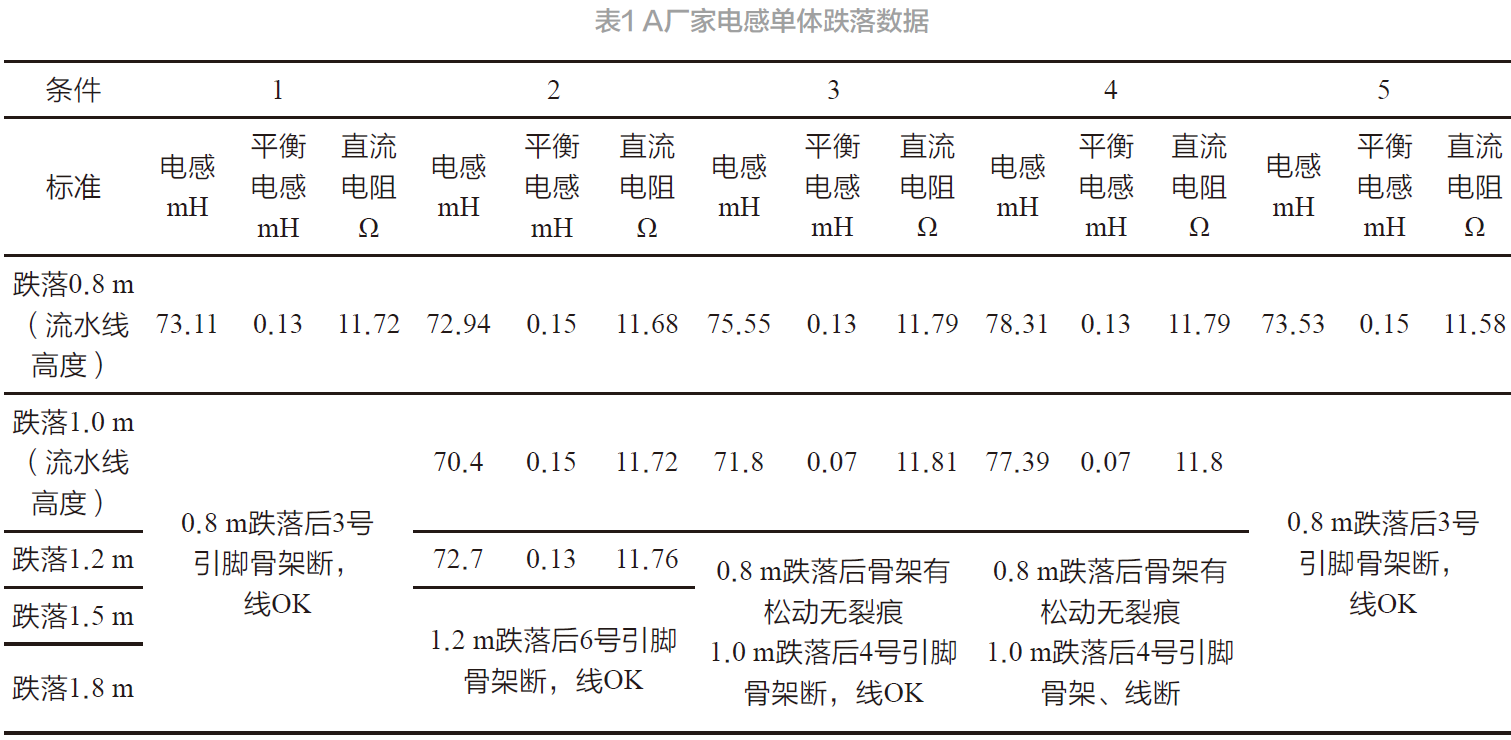

為了研究不同LPCVD TEOS薄膜厚度對Vt漂移性能的影響,我們根據表1中所示的目標厚度要求相應地調整工藝沉積時間,以在DOE晶圓上沉積不同厚度的TEOS薄膜。通過利用E+H MX204-8-37非接觸式晶圓測量儀,獲取DOE晶圓上晶圓基片厚度、TEOS制程之前的晶圓彎曲度(前彎曲度)、以及TEOS制程之后的晶圓彎曲度(后彎曲度)測量數據。然后利用該信息計算沉積不同厚度的TEOS薄膜層對DOE晶圓造成的應力。

結果和討論

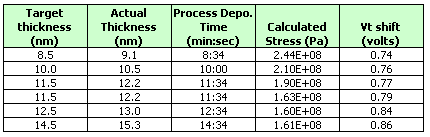

圖2表明,LPCVD TEOS薄膜厚度與Vt漂移之間具有關聯性——假設A區的數據點可能受到其他制程的影響。接下來,開展LPCVD TEOS薄膜厚度實驗驗證數據。來自3個DOE批次的實驗結果表明,LPCVD TEOS薄膜厚度與Vt漂移之間存在關聯:TEOS薄膜厚度越小,Vt漂移越小。對每個DOE批次展開進一步研究發現,如圖3b所示, Vt漂移對薄膜厚度的敏感度因批次而異,它證實了之前作出的Vt漂移可能受到除LPCVD TEOS薄膜厚度之外的其他制程影響這一假設。然而,3個DOE批次的實驗數據在LPCVD TEOS厚度對Vt漂移有影響這一點上是一致的。

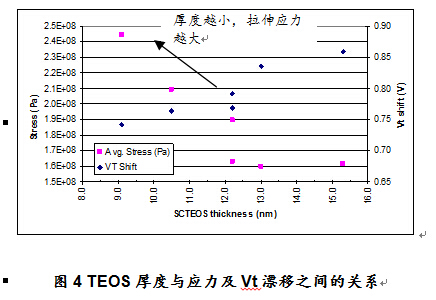

發現LPCVD TEOS厚度與閃存循環之間的關聯性是非常有益的,因為這個被沉積的只是充當S/D植入物犧牲氧化層的12.5nm TEOS薄膜將從存儲單元上去除。因為SiN(HTN)薄膜應力對閃存循環(耐久性)的影響已非常明了,我們就對不同厚度的LPCVD薄膜應力展開評估以便加強了解。如圖4所示,LPCVD TEOS薄膜厚度越小,拉伸應力越大,從而使得Vt漂移變小。Vt漂移與LPCVD TEOS薄膜厚度之間存在這種關系是因為,在LPCVD TEOS薄膜沉積時,它會引起制程應力,也就是所謂的應力記憶技術(SMT)——圖5。拉伸應力越大,產生的界面陷阱越少,循環Vt漂移也越小。該論點得到參考文獻[2]的進一步證實,它利用電荷泵(CP)法發現,因為與基片表面平行的壓縮應力,存儲單元中的編程/擦除(P/E)循環會產生更多界面陷阱(請參見圖6)。而壓縮薄膜上Tox/Si基片之間俘獲的界面越多,Vt漂移就越大。

評論