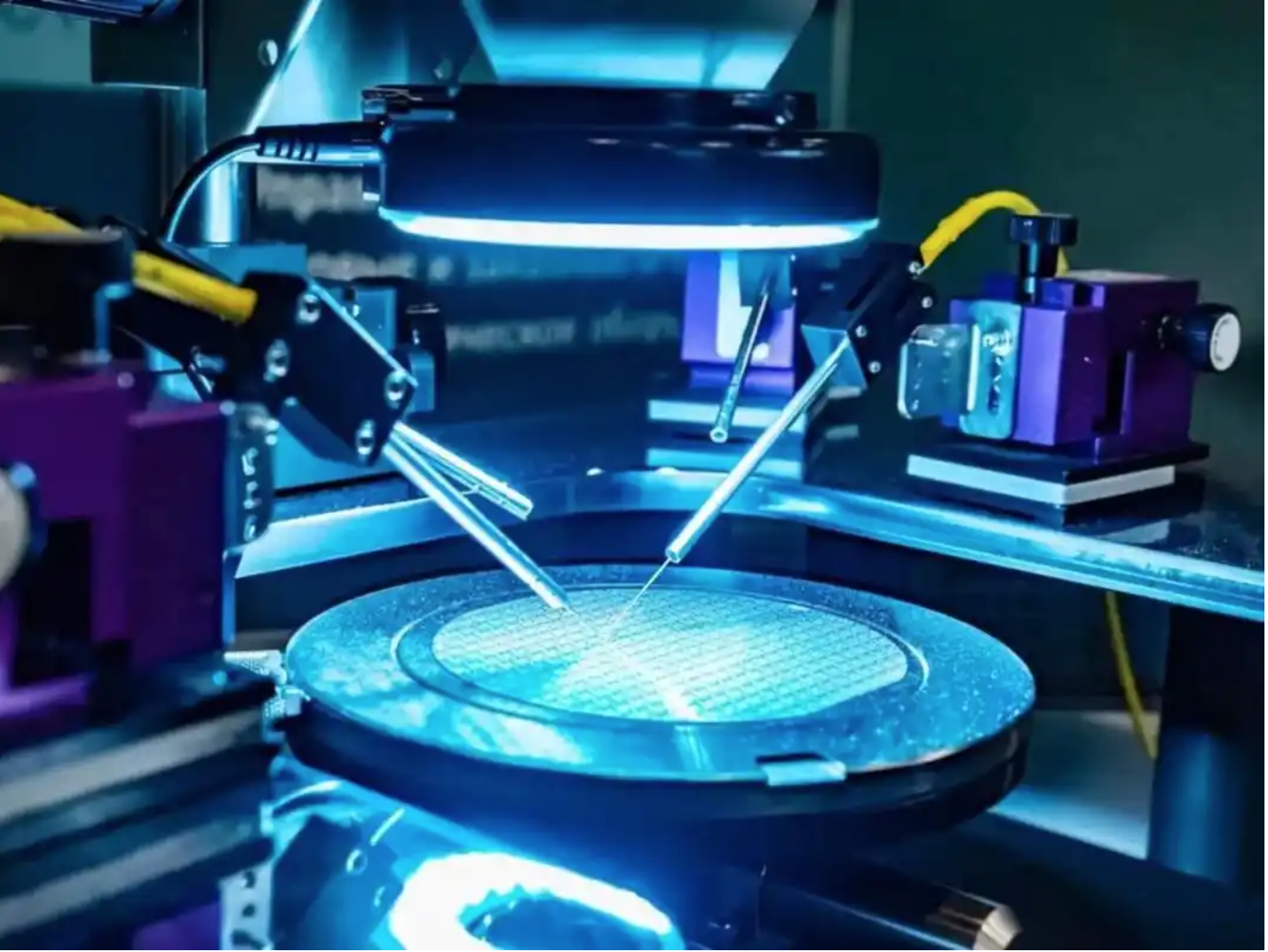

應用材料公司推出整合的高K介電常數

——

從45納米的邏輯芯片開始,由于晶體管的尺寸太小,傳統的柵極材料無法使用,過多的漏電流使晶體管發熱并消耗額外的能量。HK/MG結構可以降低柵極漏電流100多倍,并大大加快晶體管的開關速度。舉個例子來說,如果2006年付運的所有微處理器都采用了HK/MG技術,那么一年下來所節約的電能(按照每天使用12小時估算)約等于450萬戶家庭一年的用電量。使用新的HK/MG材料可以減少晶體管功耗,從而降低使用溫度,提高晶體管性能,但是這僅僅解決了問題的一部分。真正的挑戰在于如何將HK/MG材料整合到器件中,創造出具有原子級工藝界面并能滿足規模化制造要求的最優的柵極結構。

應用材料公司資深副總裁、硅系統業務部總經理Tom St. Dennis表示:“多年以來,整合新的柵極材料是我們客戶在技術延展上碰到的最艱難的障礙。我們提供已被整合驗證的HK/MG技術,使客戶能夠提高晶體管的速度,幫助他們把風險降到最小。應用材料公司歷來都能非常成功的幫助客戶將新材料整合到工藝流程中,最近的一次是在銅互聯工藝中使用低K介電常數技術。由于我們擁有相關的上下游技術,所以我們有能力優化工藝順序并幫助客戶成功整合HK/MG技術用于生產最先進的晶體管。”

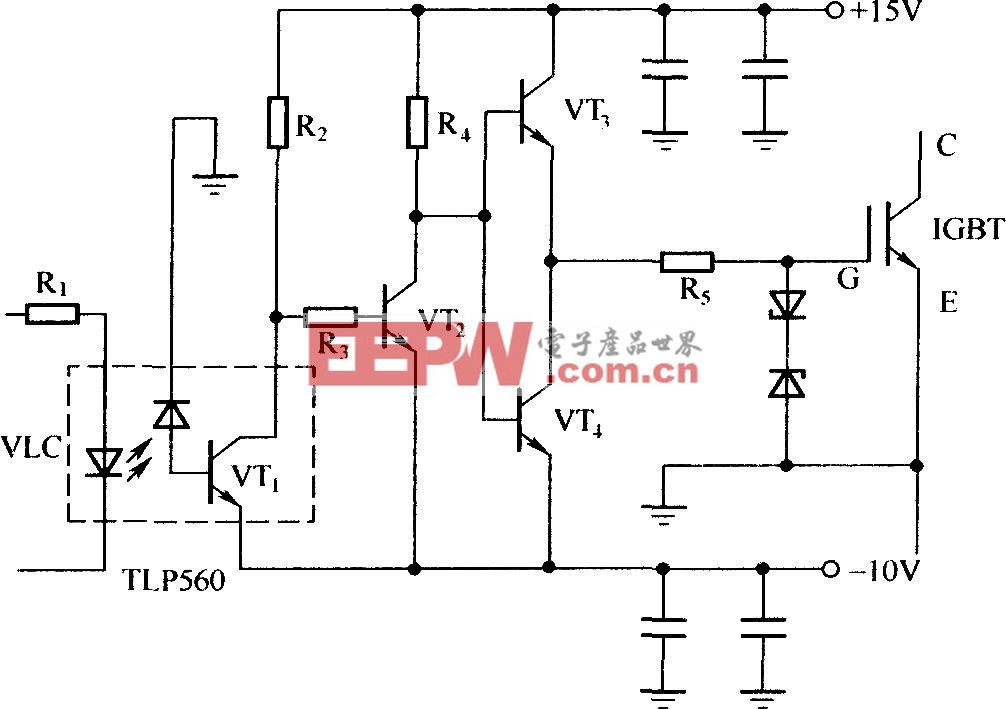

制造HK/MG結構的方法有很多種,應用材料公司有一系列可靠的系統支持客戶所使用的不同的制造方法。這些已被完全驗證的工藝經過了整合測試,可以減少客戶的調試時間,達成全面優化的HK/MG結構。應用材料公司提供的不僅僅是高K介電常數薄膜,而是基于單個Centura®平臺的整合的電介質疊合層解決方案,它包括四個關鍵的工藝——高K介質沉積、氧化、氮化和退火。在具有挑戰性的金屬柵極疊合層方面,應用材料公司運用多年來在金屬沉積上的領先技術,提供一系列基于Endura®平臺上的整合方案,使用ALD(原子層沉積)和PVD(物理氣相沉積)技術幫助客戶實現各種不同的設計。應用材料公司創新的高溫刻蝕技術能提供HK/MG疊合層生產刻蝕中至關重要的側面垂直度。應用材料公司的缺陷檢測、評價和分析系統具有25納米的缺陷靈敏度和自動FIB(聚焦離子束),可以加快對HK/MG結構的關鍵缺陷和工藝的研究進程。

評論