時鐘技術的未來發展:向分組網絡轉型(06-100)

——

就時鐘技術而言,改進的 PLL 必須鎖定于來自時鐘卡的傳統 TDM 頻率,并同時生成 TDM 時鐘頻率和分組時鐘頻率(如25 MHz)。就性能而言,用于物理層同步的分組時鐘頻率比單純的 TDM 頻率對抖動性能的要求更高。抖動生成與衰減會對改造的PLL提出更高要求。

本文引用地址:http://cqxgywz.com/article/81182.htm從背板到網絡接口存在許多可能的時鐘路徑。首先,改進的 PLL 可為 FE/GE PHY生成 25 MHz 頻率,以實現物理層同步。其次,改進的 PLL 還能為 CESoP 或 VoIP處理器生成 8 kHz 或 1.544 MHz/2.048 MHz 頻率,進而為分組網絡生成帶嵌入時鐘信息的分組。

從網絡到背板也存在多種可能的時鐘路徑。首先,FE/GE PHY 可從物理線路提取頻率為 25 MHz 或 125 MHz的時鐘,進而分解為 8 kHz 頻率并提供給背板上的時鐘卡。其次,CESoP 或 VoIP 處理器能根據帶嵌入時間戳的傳送進來的分組進行自適應時鐘恢復,從而為背板提供參考時鐘。

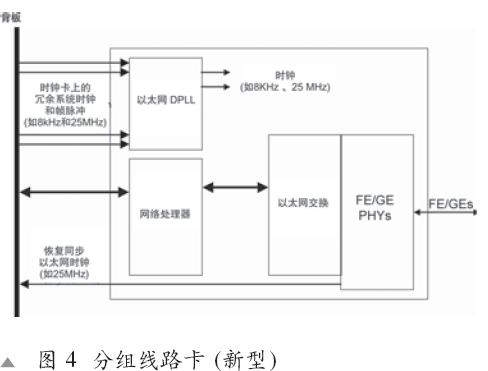

分組線路卡(新型)

圖4 給出了不帶傳統 TDM 背板且完全采用分組技術的設備。在此情況下,時鐘很可能完全采用 25 MHz (或其倍數)的頻率。這里給出的結構圖顯示了帶 GE/FE接口的分組線路卡。

評論