利用頻域時鐘抖動分析加快設計驗證過程(07-100)

—— 利用頻域時鐘抖動分析加快設計驗證過程

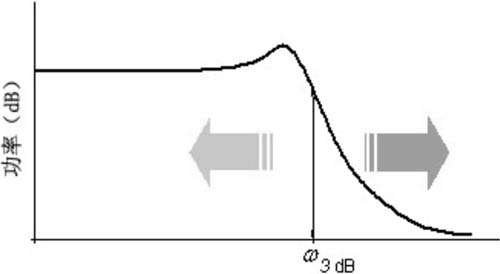

圖3 PLL頻率響應

真實的抖動源

如果觀察實際環境中的高速數字電路,您會發現許多抖動源,如圖4所示。跟我們前面討論的一樣,時鐘信號通常分配給多個IC,時鐘頻率可能進行乘法和/或除法運算。假設來自晶體振蕩器的參考時鐘具有較低的抖動,因為IC帶來的附加噪聲或其他設備產生的干擾,所以經過乘法或除法運算的輸出時鐘也可能不是非常干凈。

一個主要污染源就是開關電源的噪聲。開關頻率一般為100 kHz到1 MHz。開關電源噪聲可能會注入時鐘信號線路,它在左下圖中顯示為PJ。

其他周期抖動分量的來源可能是數據或時鐘線路的干擾,經互調后可能位于時鐘線上,也顯示為PJ分量。只要PJ分量表現的遠離時鐘頻率,它就極有可能插入帶通濾波器(或低通濾波器)來消除這些抖動。然而,問題是周期抖動在什么時間接近時鐘頻率,因為高頻高Q濾波器很難得到。參考時鐘的RJ也一樣,時鐘除法器可能添加寬帶噪聲,這可能會使輸出時鐘信號的RJ增加。

要診斷各種問題,設計人員必須表征有關電路物理布局和/或工作環境下的時鐘抖動。

評論