利用頻域時鐘抖動分析加快設計驗證過程(07-100)

——

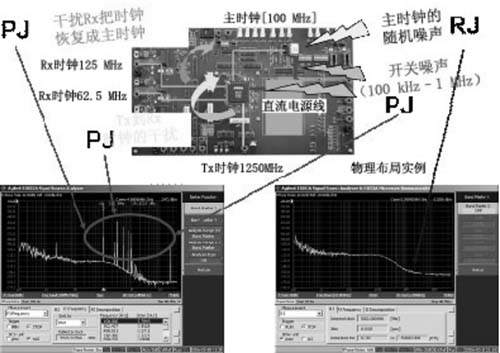

圖4 實際環境中的抖動源

全面分析時鐘信號要求達到飛秒級精度,只有相位噪聲測量技術才能達到這種精度。相位噪聲分析提供兩種主要測量:S?(f?)和?(t),它們根據相位噪聲測量帶寬限制收集時鐘的所有相位信息。

在相位噪聲分析儀上分析RJ可以完成兩個重要目標。首先,通過集成RJ頻譜,可以提取預定帶寬中的相應RJ高斯分布寬度。其次,通過分析S?(f?)的冪級數行為確定RJ的主要原因(圖5)。

在相位噪聲頻譜中可以看到PJ分量的雜散。所以PJ頻率知識對于診斷問題非常有幫助。參考每個PJ頻率的PJ rms也能幫您了解每個PJ分量對總體時鐘抖動的影響,查看去除主要PJ分量之后總體抖動的變化(圖6)。

圖5 分析相位噪聲測量的RJ

評論