“設計 文章 最新資訊

Cadence推出SPB 16.2版本應對小型化產(chǎn)品設計挑戰(zhàn)

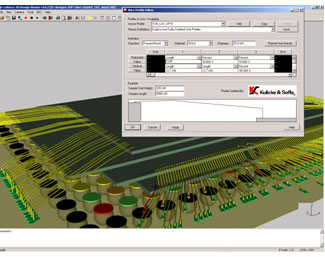

- Cadence發(fā)布了SPB 16.2版本,全力解決電流與新出現(xiàn)的芯片封裝設計問題。這次的最新版本提供了高級IC封裝/系統(tǒng)級封裝(SiP)小型化、設計周期縮減和DFM驅(qū)動設計,以及一個全新的電源完整性建模解決方案。這些新功能可以提高從事單芯片和多芯片封裝/SiP的數(shù)字、模擬、RF和混合信號IC封裝設計師的效率。 設計團隊將會看到,新規(guī)則和約束導向型自動化能力的推出,解決了高密度互連(HDI)襯底制造的設計方法學問題,而這對于小型化和提高功能密度來說是一個重要的促進因素,因而得以使總體的封裝尺寸大大

- 關(guān)鍵字: 封裝 設計 Cadence SPB

設計下一代自動化測試系統(tǒng)

- 測試管理人員和工程師們?yōu)榱吮WC產(chǎn)品的質(zhì)量和可靠性,從設計驗證,生產(chǎn)線測試到設備維修診斷,從簡單的通過/失敗測試應用,到執(zhí)行全套的產(chǎn)品特性測試,都離不開自動化測試系統(tǒng)的設計與構(gòu)建。本文要討論的下一代自動化測試系統(tǒng)正是基于測試測量行業(yè)發(fā)展的趨勢和工程師團隊所面臨的挑戰(zhàn),通過構(gòu)建以軟件為核心的模塊化系統(tǒng)架構(gòu)幫助工程師們以創(chuàng)新的思維提高測試效率,滿足用戶自定義的需求。

- 關(guān)鍵字: 測試系統(tǒng) 自動化 下一代 設計

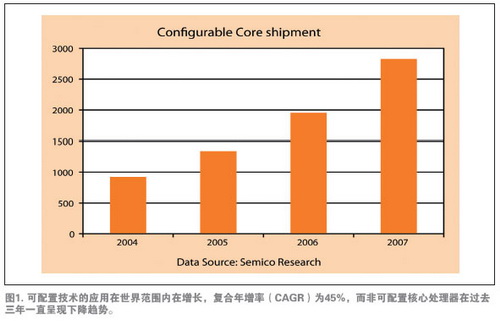

可配置技術(shù)影響SoC(系統(tǒng)級芯片)的設計

- 傳統(tǒng)上,系統(tǒng)級芯片(SoC)設計師必須應對剛性的非可配置核心技術(shù)。眾所周知,傳統(tǒng)的核心工藝在設計或制造過程中是不可配置的,并且不能按多種用途進行定制。反過來,這些工藝產(chǎn)生了如下的迫切需要:將定制程序包括進處理器,配置多種應用,能進行軟件開發(fā)的綜合工具,簡化機器語言編程。 隨著可配置的核心處理器的出現(xiàn),SoC設計有望發(fā)生重大變化來改變這些設計問題。影響SOC設計能力的主要益處有:降低開發(fā)成本,減少芯片的重新設計、進入各類垂直市場更快,性能的獨特性和設計的靈活性,同時不損害系統(tǒng)的特性和性能。此外,S

- 關(guān)鍵字: SoC 系統(tǒng)級芯片 設計 配置 H264

“設計介紹

您好,目前還沒有人創(chuàng)建詞條“設計!

歡迎您創(chuàng)建該詞條,闡述對“設計的理解,并與今后在此搜索“設計的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對“設計的理解,并與今后在此搜索“設計的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司