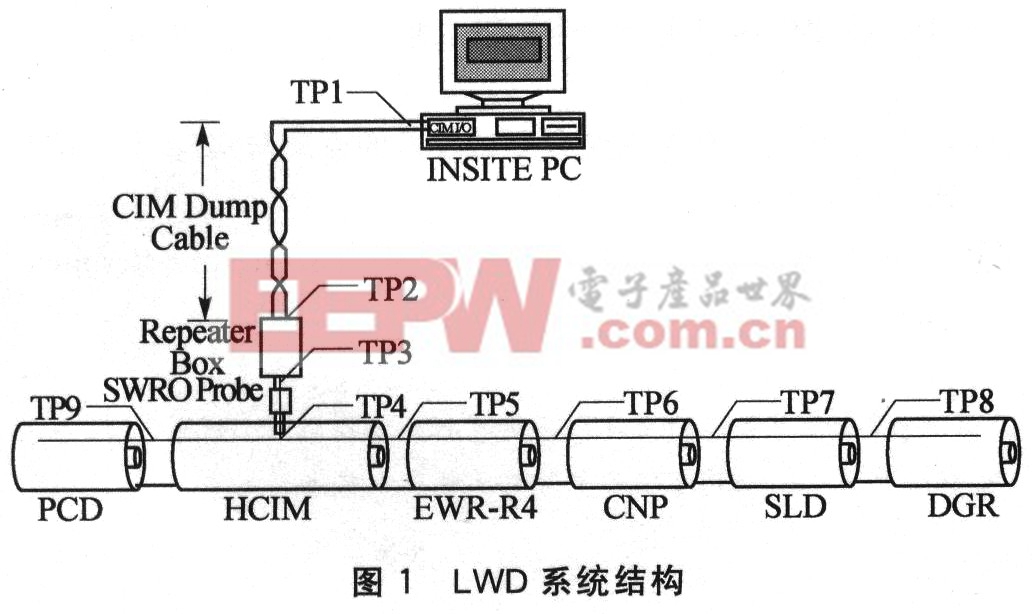

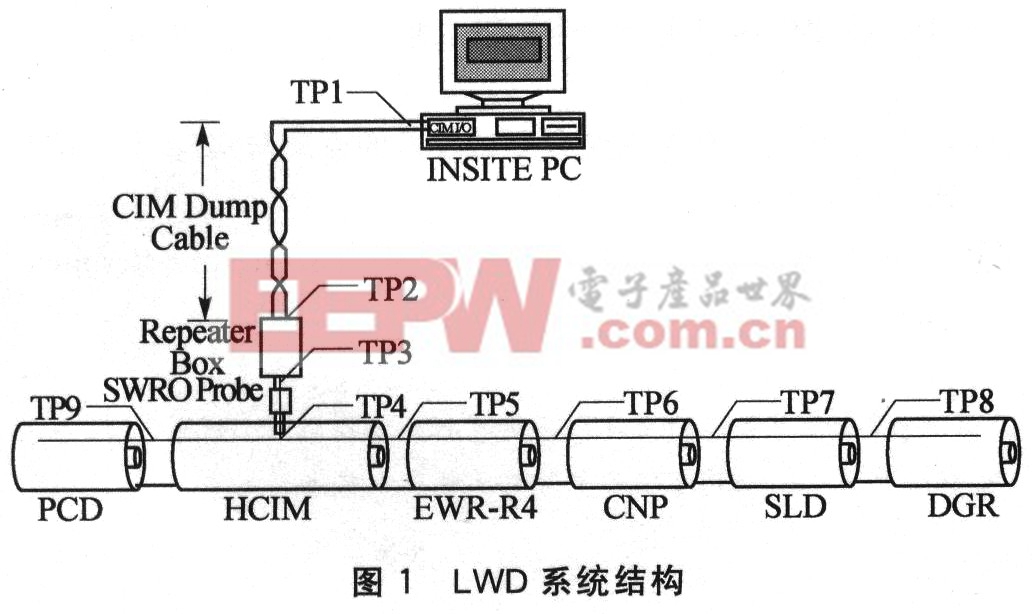

- 提出了隨鉆測井系統井下傳感器的一種低功耗設計方法。介紹了隨鉆測井系統,其需要在井下長時間工作且只能通過電池供電的特殊性,決定了低功耗設計是整個系統設計的核心問題。本文通過對低功耗電路設計原則的分析,結合隨鉆測井系統的要求,采用Freescale公司的MC9S12Q128單片機,在硬件和軟件兩個方面對隨鉆測井系統井下傳感器進行了低功耗設計,采用低功率器件和動態功耗分配的省電管理模式。

- 關鍵字:

設計 井下 系統 測井 單片機 傳感囂 低功耗 ADC

- 1 引言

單片機(或微控制器)技術已滲透到生活的方方面面,廣泛應用于家用電器、通信、測試等領域。因此該技術正積極影響著人們的生活。這里給出一種基于MSP430單片機的測試系統設計。MSP430系列單片機是TI公司生

- 關鍵字:

應用 測試系統 單片機 MSP430 低功耗 存儲

- 在分析Cache性能的基礎上介紹了當前低功耗Cache的設計方法,提出了一種可重構Cache模型和動態可重構算法。Cache模型能夠在程序運行過程中改變相聯度和大小,動態可重構算法能夠在運行時針對不同的應用程序對可重構Cache進行配置。通過對Cache的動態配置,不僅可以提高Cache命中率,還能夠有效降低處理器的功耗。

- 關鍵字:

Cache 低功耗 可重構 技術研究

- 世界領先的微控制器廠商意法半導體宣布,首批整合其高性能8位架構和最近發布的超低功耗創新技術的8位微控制器開始量產。以節省運行和待機功耗為特色,STM8L系列下設三個產品線,共計26款產品,涵蓋多種高性能和多功能應用。

設計工程師利用全新的STM8L系列可提高終端產品的性能和功能,同時還能滿足以市場為導向的需求,例如,終端用戶對節能環保產品的需求,便攜設備、各種醫療設備、工業設備、電子計量設備、感應或安保設備對電池使用周期的要求。設計人員將選擇STM8L這類超低功耗的微控制器,以符合低功耗產品設計

- 關鍵字:

ST 微控制器 低功耗

- 全球電子設計創新領導廠商Cadence益華電腦今天宣布,創意電子(Global Unichip Corporation,GUC)將以CPF為基礎的Cadence低功耗解決方案,整合至其PowerMagic設計方法中,協助客戶將復雜的低功耗ASIC設計實現最佳化。

創意電子在PowerMagicTM設計方法,針對ASIC設計驗證與實現,整合Cadence®低功耗解決方案 (包括Cadence Encounter® RTL Compiler、Encounter 數位設計實現系統(ED

- 關鍵字:

Cadence PowerMagic 低功耗 EDI

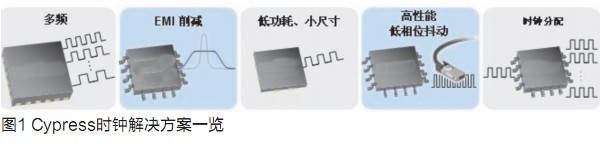

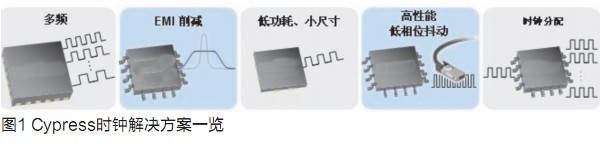

- 時鐘按功能分,可分為多頻、EMI削減、低功耗小尺寸、高性能低相位抖動、時鐘分配等(如圖1)。

多頻:就是在同一個晶振里可產生不同頻率的時鐘源。例如,晶振本身也許是一個37kHz的,你可以從這個頻率上面去延伸開來,像ATM需要25MHz,SDH需要19.44MHz……這一個器件可產生系統里需要的所有頻率,并且這些頻率之間可以相互沒有任何關系。

EMI削減:該器件已擁有多頻器件的所有功能,除此之外,EMI(電磁干擾)削減特點突出。

低功耗、小尺寸:主要針對

- 關鍵字:

Cypress 時鐘 EMI 低功耗

- 1 引言

通用串行總線USB(Universal Serial Bus)接口以其通信速率快,USB2.0協議速率達480 Mb/s,支持熱插拔的特點得到廣泛應用,緩解日益增加的PC外設與有限的主板插槽和端口之間的矛盾;而低壓差分信號LVDS(

- 關鍵字:

轉換器 接口 LVDS USB 簡易 USB,低功耗

- 1 引言

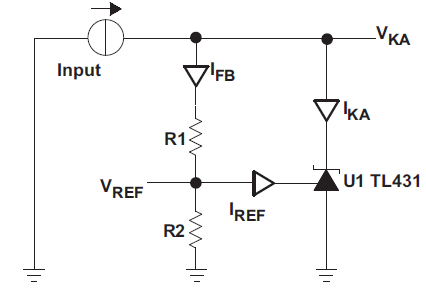

在低功耗設備中,供電穩定性是影響設備性能的關鍵因素之一,高效的電源備份系統可為低功耗設備提供穩定的電源管理性能和靈活的供電配置選擇。因此,這里提出一種基于MAX16024的低功耗設備電源備份方案。

- 關鍵字:

備份 方案 電源 設備 MAX16024 功耗 基于 低功耗,電源

- 基于嵌基于μC/OS-II嵌入式實時操作系統的低功耗開發, 隨著嵌入式系統應用的日益廣泛,如何實現嵌入式系統的低功耗開發已經成為嵌入式應用發展的關鍵技術之一,是近幾年來人們在嵌入式系統的設計中普遍關注的難點與熱點。嵌入式系統正被廣泛應用于移動性較強的產品中去

- 關鍵字:

操作系統 實時 C/OS-II 嵌入式 低功耗

- 引言

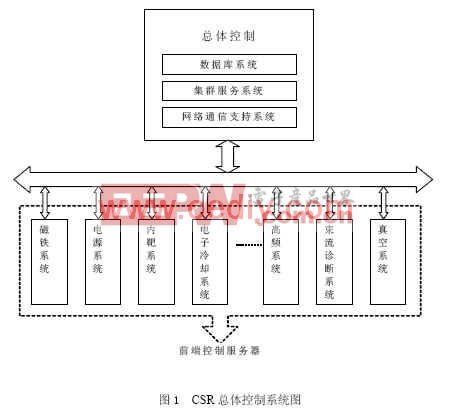

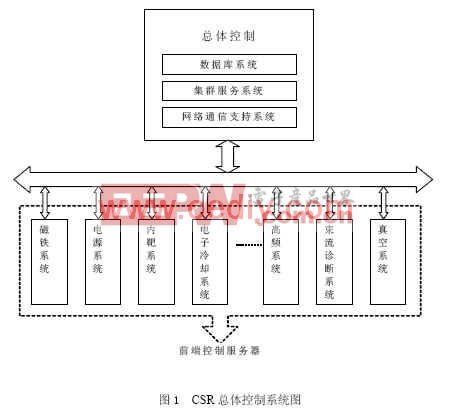

HIFRL-CSR中磁場的作用是約束離子行為,帶電粒子束在磁場中聚焦和傳輸,磁場性能的好壞直接影響到束流的品質,而磁鐵溫度又影響著磁場的安全性能。在加速器控制系統中,放置在CSR主環的磁鐵多達40多個,要對其

- 關鍵字:

設計 系統 溫度 磁鐵 CSR 單片機 C語言 低功耗

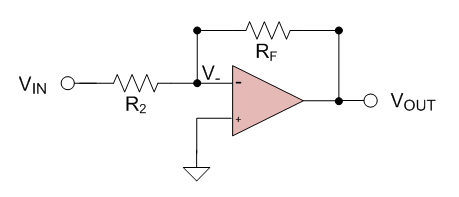

- 介紹了一個用于高精度模數轉換器,采用0.25μmCMOS工藝的高性能采樣保持電路。該采樣保持電路的采樣頻率為20MHz,允許最大采樣信號頻率為10MHz,在電源電壓為2.5V的情況下,采樣信號全差分幅度為2V。通過采用全差分flip-around結構,而非傳統的電荷傳輸構架,因而在同等精度下,大大降低了功耗。為了提高信噪比,采用自舉開關。Hspice仿真結構顯示:在輸入信號為5MHz的情況下,無雜散動態范圍(SFDR)為92.4dB.該電路將被用于一個14位20MHz流水線模數轉換器。

- 關鍵字:

流水線 高精度 低功耗 采樣保持電路

- 引言

壓控振蕩器(VCO,Voltage-Controlled Oscilla-tor)作為射頻集成電路中的一個關鍵性部件,隨著無線技術的快速發展而必須滿足新的性能要求。目前,無線收發機發展的方向之一就是兼容兩個或多個通信頻段。即要

- 關鍵字:

耦合 低功耗,射頻

- 芯片設計解決方案供應商微捷碼(Magma®)設計自動化有限公司日前宣布,一款支持新加坡特許半導體制造公司新一代增強的65納米低功耗工藝的基于Common Platform技術、基于Talus®的低功耗RTL-to-GDSII集成電路(IC)設計流程正式面市。這項增強的65納米低功耗工藝被簡稱為65nm LPe;它通過利用創新性減少漏電技術,可顯著降低高達50%的片上系統(SoC)待機功耗。

基于微捷碼Talus IC實現系統,這款支持Chartered 65LPe的低功耗參考流程

- 關鍵字:

Magma Talus 65納米 低功耗

- 對便攜式系統設備而言,在采用目前90 nm和130 nm工藝進行新的系統級芯片(SoC)設計中,對整個系統功耗的優化變得與性能和面積的優化同等重要。為此,簡單介紹了涵蓋靜態功耗和動態功耗的低功耗技術,同時提供了一種能夠通過使用前向預測反饋的動態電壓頻率調節(DVFS)系統,并對該技術的可行性進行了建模分析,驗證了自適應DVFlS方式的有效性,同時也給出了評估DVFS仿真的有效途徑。

- 關鍵字:

DVFS SoC 低功耗 技術研究

低功耗介紹

如果用實實在在的詞語來表達,那就是:這些特點減少了一個終端系統的總功耗,而這反過來又有望降低我們對于化石燃料的依賴。由于可以將較低的功耗直接視為等同于所需電力的減少,因此使得上述目標得以實現。而且,較少的電力消耗首先意味著產生電能所需的化石燃料的減少。相應地,這將有助于減少對于我們所居住星球的大氣和氣候具有負面影響的溫室氣體。

為了進一步說明這一點,考慮一下,美國每年總耗電量大約為 4 萬億 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473