聯(lián)電 文章 最新資訊

晶圓代工廠聯(lián)電公布最新財報 產業(yè)進入庫存調整期

- 近期,半導體晶圓代工廠聯(lián)電公布最新財報,公司11月營收225.45億元新臺幣,相較去年同期的196.61億元新臺幣增加14.67%,環(huán)比減少7.39%,連續(xù)三個月出現(xiàn)衰退;累計2022年前11月合并營收2577.59億元新臺幣,相較去年同期的1927.31億元新臺幣增加了33.74%。據中國臺灣《經濟日報》報道,聯(lián)電總經理王石此前在法說會上預估,第四季度晶圓出貨量將減少約10%,產品平均售價持平,毛利率將約41%至43%,產能利用率恐將降至90%,11月營收呈現(xiàn)月減,符合法說會提出產業(yè)進入庫存調整的預期。

- 關鍵字: 晶圓代工廠 聯(lián)電

聯(lián)電與Cadence共同開發(fā)認證的毫米波參考流程達成一次完成硅晶設計

- 聯(lián)華電子與全球電子設計創(chuàng)新領導廠商益華計算機(Cadence Design Systems, Inc.)于今(30)日宣布雙方合作經認證的毫米波參考流程,成功協(xié)助亞洲射頻IP設計的領導廠商聚睿電子(Gear Radio Electronics),在聯(lián)電28HPC+ 制程技術以及Cadence? 射頻(RF)解決方案的架構下,達成低噪音放大器 (LNA) IC一次完成硅晶設計(first-pass silicon success) 的非凡成果。 經驗證的聯(lián)電28HPC+解決方案非常適合生產應用于高

- 關鍵字: 聯(lián)電 Cadence 毫米波參考流程

聯(lián)電 啟動供應鏈碳盤查計劃

- 聯(lián)電9日舉行年度供貨商大會,宣布正式啟動「供應鏈碳盤查輔導計劃」,提供顧問資源平臺與工具,攜手供貨商進行溫室氣體盤查及管理,預計至2030年完成500家供貨商碳盤查輔導作業(yè)。聯(lián)電供貨商大會總計有超過200家供貨商熱情響應及參與。現(xiàn)場的低碳供應鏈宣誓儀式,除聯(lián)電總經理簡山杰、副總廖木良及資材處協(xié)理謝集國代表外,也邀請環(huán)球晶、美日先進光罩(PDMC)、默克、應用材料、科磊(KLA)等廠商一同宣誓,希望結合供貨商伙伴的力量,邁向整體供應鏈2030年達到減碳20%目標。聯(lián)電為協(xié)助供貨商建立碳盤查能力,預計將投入新

- 關鍵字: 聯(lián)電 供應鏈 碳盤查

聯(lián)電看后市 明年Q2觸底回升

- 晶圓代工大廠聯(lián)電受惠于產能滿載及新臺幣貶值,第三季合并營收753.92億元續(xù)創(chuàng)歷史新高,第四季因客戶進行庫存去化而減少投片,預期產能利用率將出現(xiàn)下滑,明年第一季有機會觸底并在第二季回升。聯(lián)電21日宣布,獲英飛凌最佳晶圓代工獎肯定,未來將在車用電子、5G、人工智能物聯(lián)網(AIoT)等領域擴大合作。聯(lián)電并在吉隆坡舉行的英飛凌2022年全球供貨商活動中,獲得英飛凌最佳晶圓代工獎,肯定聯(lián)電在近期供應鏈中斷情況下,持續(xù)致力于卓越制造并堅定履行對客戶承諾的貢獻。英飛凌營運長Rutger Wijburg表示,感謝過去兩

- 關鍵字: 聯(lián)電 英飛凌 晶圓代工

聯(lián)電與Cadence攜手22納米模擬與混合信號設計認證

- 聯(lián)華電子與Cadence于今(8月24)日共同宣布,Cadence的模擬與混合信號(Analog/Mixed Signal, AMS)芯片設計流程獲得聯(lián)華電子22納米超低功耗 (22ULP)與22納米超低漏電(22ULL)制程認證,此流程可優(yōu)化制程效率、縮短設計時間,加速5G、物聯(lián)網和顯示等應用設計開發(fā),滿足日漸增高的市場需求。 聯(lián)電的22納米制程具有超低功耗和超低漏電的技術優(yōu)勢,可滿足在科技創(chuàng)新發(fā)展下,使用時間長、體積小、運算強的應用需求。經聯(lián)電認證的Cadence AMS設計流程,提供了整合

- 關鍵字: 聯(lián)電 Cadence 22納米 模擬與混合信號

聯(lián)電科學基礎減碳目標 領先晶圓專工業(yè)通過SBTi審核

- 氣候極端變化的危機步步逼近,如何阻止地球升溫已是全球關注的課題。聯(lián)華電子今(23)日宣布,針對氣候調適議題所設定的減碳路徑,已通過國際科學基礎減碳目標倡議(SBTi)審核,為全球第一家通過的半導體晶圓專工業(yè)者。這是聯(lián)電繼2021年宣示2050年凈零排放后,再次領先業(yè)界通過審查,為達成凈零目標邁出重要一步。 聯(lián)華電子共同總經理暨永續(xù)長簡山杰表示:“聯(lián)電在去(2021)年宣示2050年凈零排放承諾,此次通過科學基礎減碳目標(SBT)的審核,正是為達成凈零排放確定路徑,更確立我們的目標與國際趨勢一致。

- 關鍵字: 聯(lián)電 晶圓

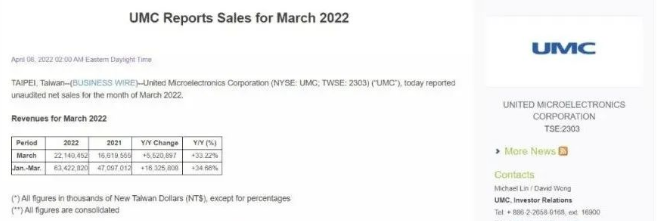

臺積電與臺聯(lián)電在2022年Q1代工收入增長均達35%

- 據國外媒體報,當前全球最大的晶圓代工商臺積電,已經披露了他們3月份的營收,一季度的營收也隨之出爐,達到了4910.76億新臺幣,也就是接近170億美元,達到了預期,也再次創(chuàng)下新高。在過去的一年多里,全球對各種芯片的需求量都非常高,以至于各大晶圓代工廠紛紛提高了芯片制造的報價,不同制程節(jié)點的價格已多次上漲。臺積電(TSMC)作為全球最大的晶圓代工廠,產能上有著絕對的優(yōu)勢,而且有著競爭對手無法提供的技術。隨著產能和報價不斷提高,臺積電在2022年第一季度的業(yè)績創(chuàng)下了歷史新高。根據臺積電公布的最新財報,2022

- 關鍵字: 臺積電 聯(lián)電 代工

傳聯(lián)電擬斥資1000億新臺幣在新加坡建新12英寸晶圓廠

- 集微網消息,近日市場有消息稱聯(lián)電計劃投資逾1000億元新臺幣在新加坡建設第二座12英寸晶圓廠,月產能至少2萬~3萬片,或生產40nm以下制程的芯片。 據鉅亨網報道,聯(lián)電對此回應稱,新加坡本來就有設廠,在全球有據點的地方持續(xù)評估建廠規(guī)劃,不過目前還沒有確切地點。 據了解,聯(lián)電新加坡廠Fab 12i位于白沙晶圓科技園區(qū),于2004年開始量產,月產能為5萬片,制程為0.13微米至40nm,產品涵蓋FPGA、無線通訊芯片等。 業(yè)界人士認為,聯(lián)電此次可能采40nm以下制程,如28nm制程生產芯片。 據悉

- 關鍵字: 聯(lián)電 晶圓廠 芯片

芯片漲價潮不斷,聯(lián)電、中芯國際等三季度或再提高晶圓報價

- 據臺灣供應鏈媒體Digitimes報道,主要晶圓代工廠聯(lián)電、世界先進、力積電、中芯國際、格芯都將計劃再次提高其晶圓代工報價,以應對持續(xù)緊張的產能。報道稱,消息人士指出,第三季度晶圓代工廠報價的計劃漲幅將高于今年上半年,包括8英寸和12英寸晶圓。此外,臺積電已取消了今年新訂單以及2022年訂單的所有價格折扣,等同于漲價。隨著代工價格進一步上漲,預計晶圓代工廠將在第三季度發(fā)布旺盛的營收和利潤。該知情人士還指出,目前客戶排隊等待晶圓代工廠產能,其中8英寸晶圓代工廠更是客戶緊盯的重中之重。然而,雖然臺積電、聯(lián)電、

- 關鍵字: 芯片漲價 聯(lián)電 中芯國際 晶圓

聯(lián)電28nm成熟制程準備繼續(xù)擴產,找上三大IC設計公司合作投資

- 眾所周知,目前全球最為緊缺的是28nm及以上的成熟制程的晶圓代工產能,近日臺積電已宣布將投入28.87億美元資本支出擴充成熟制程,其中南京廠將擴產28nm產能至每月4萬片。同樣,聯(lián)電也準備積極的擴產28nm成熟制程產能。4月24日消息,據臺灣媒體報道稱,晶圓代工大廠聯(lián)電正與包括聯(lián)發(fā)科、聯(lián)詠、瑞昱等3大IC 設計公司討論投資產能合作的情況,以進一步滿足現(xiàn)階段的市場需求。報道指出,在當前電源管理芯片、顯示驅動芯片、汽車電子芯片等產品市場供應吃緊,交貨期持續(xù)拉長的情況下,顯示出這些主力以28nm成熟制程生產的產

- 關鍵字: 聯(lián)電 28nm

聯(lián)電獲準100%併購 日本三重富士通半導體

- 晶圓代工廠聯(lián)電25日宣布,已獲得最終批準,將購買與富士通半導體(FSL)所合資的12吋晶圓代工廠三重富士通半導體(MIFS)全部股權,完成併購的日期訂定于2019年10月1日。聯(lián)電表示,近年來國際政治情勢朝向保護主義發(fā)展,聯(lián)電併購MIFS晶圓廠時間長達一年余,中間經歷了日本及相關政府機構的嚴格審查,所幸最后仍獲最終核準,將MIFS納入成為聯(lián)電100%持股子公司。在完成併購后,聯(lián)電不僅在12吋晶圓月產能增加3萬多片,擴大日本半導體市場版圖,在晶圓代工市占率將重回第二大,并提升臺灣在全球半導體及晶圓代工市場影

- 關鍵字: 聯(lián)電

Cadence與聯(lián)電合作開發(fā)28納米HPC+工藝中模擬/混合信號流程的認證

- 聯(lián)華電子今(6日)宣布Cadence?模擬/混合信號(AMS)芯片設計流程已獲得聯(lián)華電子28納米HPC+工藝的認證。 透過此認證,Cadence和聯(lián)電的共同客戶可以于28納米HPC+工藝上利用全新的AMS解決方案,去設計汽車、工業(yè)物聯(lián)網(IoT)和人工智能(AI)芯片。 此完整的AMS流程是基于聯(lián)電晶圓設計套件(FDK)所設計的,其中包括具有高度自動化電路設計、布局、簽核及驗證流程的一個實際示范電路,讓客戶可在28納米的HPC+工藝上實現(xiàn)更無縫的芯片設計。Cadence AMS流程結合了經客制化確認的類比

- 關鍵字: Cadence 聯(lián)電 28納米HPC 工藝中模擬/混合信號 流程認證

聯(lián)電介紹

臺灣聯(lián)電集團總部設在臺灣,集團旗下有5家晶圓代工廠,包括聯(lián)電、聯(lián)誠、聯(lián)瑞、聯(lián)嘉以及最新投資的合泰半導體,是全球半導體投資第四大,僅次于英代爾、摩托羅拉及西門子. 根據"經濟部中央標準局"公布的近5年島內百大"專利大戶"名單,以申請件數排名, 聯(lián)電第一、工研院第二、臺積電第三;就取得美國專利件數而言,1993年至1997年所累積的件數,聯(lián)電是臺積電的兩倍、工研院的3倍. [ 查看詳細 ]

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司