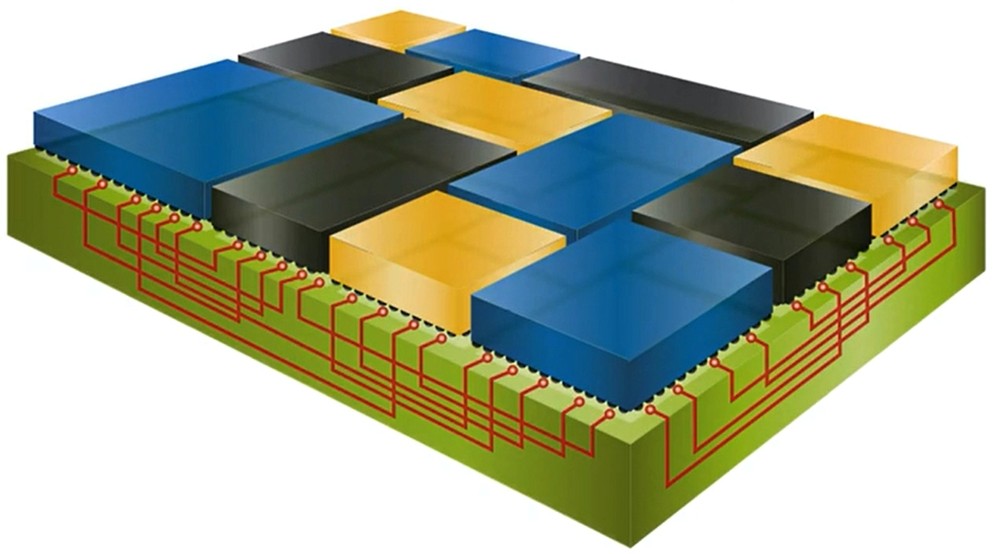

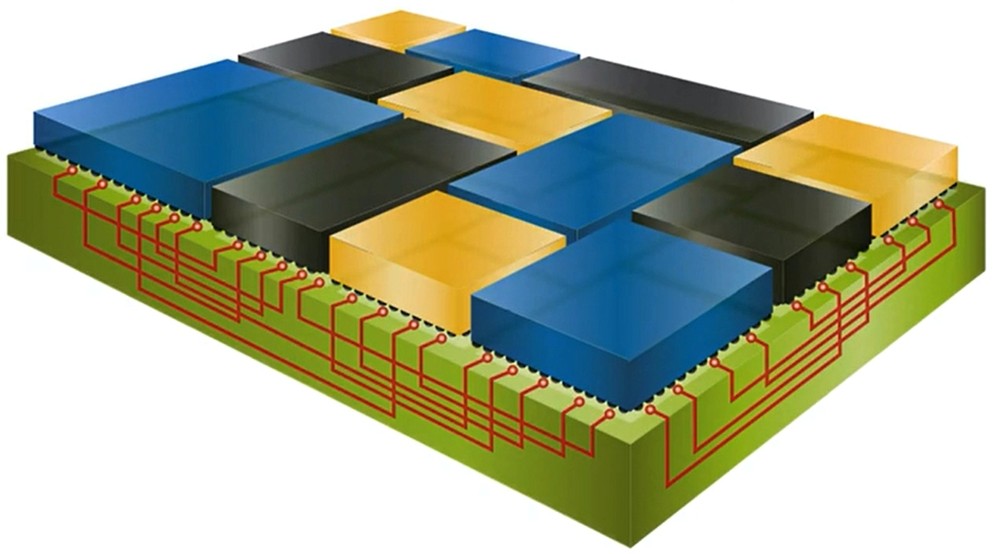

- 核心要點芯粒和三維集成電路架構產生了新的熱機械應力,可能影響整個系統的可靠性。隨著芯粒被集成至封裝中,系統內各組件的缺陷率指標要求愈發嚴苛。傳統的技術壁壘正在被打破,設計團隊不得不著手解決此前由代工廠負責的材料選擇等問題。芯粒架構在數據中心的快速普及,正推動著從芯粒設計、封裝到實際應用全流程的全方位變革。相關成本激增,可靠性擔憂加劇,以往用于控制成本、保障器件正常工作的方法已逐漸失效。行業關注的焦點不再局限于電遷移和電源完整性,還新增了隨工作負載、互連數量與類型、z 軸設計延伸范圍變化的熱機械應力問題。建

- 關鍵字:

芯粒 三維集成電路 電氣 機械挑戰 先進封裝 芯粒可靠性 西門子EDA 新思科技

- 寄生參數提取在集成電路 (IC) 設計中是必不可少的,因為它可以識別可能影響電路性能的意外電阻、電容和電感。這些寄生元件來自電路的布局和互連,會影響信號完整性、功耗和時序。隨著 IC 設計縮小到更小的節點,寄生效應變得更加明顯,因此精確提取對于確保設計可靠性至關重要。通過對這些效應進行建模,設計人員可以調整電路以保持性能,避免信號延遲或功率損耗等問題,并成功實現設計收斂。什么是寄生參數提取在半導體設計中,寄生元件(如電阻、電容和電感)是集成電路 (IC) 物理制造過程中意外但不可避免的元件。這些元素是所用

- 關鍵字:

數字設計 寄生提取 西門子EDA

- ●? ?全新?Innovator3D IC?套件憑借算力、性能、合規性及數據完整性分析能力,幫助加速設計流程●? ?Calibre 3DStress?可在設計流程的各個階段對芯片封裝交互作用進行早期分析與仿真西門子數字化工業軟件日前宣布為其電子設計自動化?(EDA)?產品組合新增兩大解決方案,助力半導體設計團隊攻克?2.5D/3D?集成電路?(IC)?設計與制造的復雜挑戰。西門

- 關鍵字:

西門子EDA 3D IC

- Siemens EDA 強調,整個半導體行業第一枚硅晶圓流片的成功率下降令人震驚。Siemens EDA(Siemens Digital Industries Software 旗下公司)設計驗證技術副總裁兼總經理 Abhi Kolpekwar 表示,首次流片成功率正在下降,從 2022 年的 24% 和 2020 年的 32% 下降到 2024 年的 14%。“這在 ASIC 和 FPGA 中都是一個令人驚訝和令人震驚的下降,”他說。這是一個非常大的問題,可以追溯到今天人們流片的設計復雜性。該公司開發了

- 關鍵字:

西門子EDA AI工具 流片成功率

- 西門子數字化工業軟件日前宣布,韓國nepes公司已采用西門子ED 的系列解決方案,以應對與3D封裝有關的熱、機械和其他設計挑戰。SAPEON韓國研發中心副總裁Brad Seo表示:“nepes 致力于為客戶提供全面的半導體封裝設計和制造服務解決方案,幫助客戶在半導體市場上獲得持續成功。今天的半導體行業對于性能和小尺寸的需求越來越高,nepes與西門子EDA的攜手將幫助我們實現發展所需的創新技術。”nepes 是外包半導體封裝測試服務(OSAT)的全球領導者,致力于為全球電子業客戶提供世界級的封裝、測試和半

- 關鍵字:

nepes 西門子EDA 3D封裝

- 8月24日,西門子EDA的年度盛會 ——?2023 Siemens?EDA Forum在上海浦東拉開帷幕。此次峰會是西門子EDA闊別三年線下之后的再度回歸,會議以“加速創芯,智領未來”為主題,聚焦AI 應用、汽車芯片、SoC、3D IC 及電路板系統技術等熱點話題,分享西門子EDA的最新技術成果,并邀請多位行業專家、技術先鋒、合作伙伴匯聚一堂,共同探討全球半導體與集成電路(IC)產業的發展趨勢與技術創新之道。作為半導體行業的基石,處于產業鏈中的最上游的EDA支撐著規模龐大的半導體市場,

- 關鍵字:

西門子EDA EDA

- 西門子數字化工業軟件近日宣布,無晶圓基板初創企業?Chipletz?選擇西門子?EDA 作為電子設計自動化(EDA)戰略合作伙伴,助其開發具有開創性的?Smart Substrate??產品。在對可用解決方案進行綜合技術評估之后,Chipletz?選擇了一系列西門子?EDA?工具,對其?Smart Substrate?技術進行設計和驗證。Smart Substrate?有助于將多個芯片集成在一個封

- 關鍵字:

Chipletz 西門子EDA Smart Substrate IC封裝

- 伴隨5G、汽車電子、人工智能及物聯網等技術的不斷發展,全球半導體產業需求也保持持續增長態勢,根據半導體行業權威機構世界半導體貿易統計協會(WSTS)發布的數據,2022年全球半導體市場預計增長16.3%。與此同時,新技術的落地與融合也進一步加速各行各業的數字化轉型,企業需要利用創新和數字化方法開拓新的市場規則,將電氣、電子、軟件和機械與智能商業環境、智能工廠、智能基礎設施等系統整合為自成一體的生態系統,從而確立和鞏固市場領導者的地位,而這不僅僅意味著作為數字化核心的半導體產業會呈現出指數級增長,同時也意味

- 關鍵字:

西門子EDA

- 處理器設計自動化領域的領導性企業Codasip近日宣布:通過采用西門子集團Siemens EDA的OneSpin IC驗證工具,擴大了其形式驗證解決方案的可用工具范圍,以進行全面和徹底的處理器測試。Codasip不斷在處理器驗證方面投入巨資,以再接再厲為業界提供最高質量的RISC-V處理器半導體知識產權(IP)。Siemens EDA的OneSpin工具提供了一個先進且無比強大的驗證平臺,用以解決關鍵的芯片完整性問題。OneSpin是極為先進的形式驗證工具,適用于汽車和其他高完整性處理器應用,能以最少的設

- 關鍵字:

Codasip 西門子EDA RISC-V 形式驗證

西門子eda介紹

您好,目前還沒有人創建詞條西門子eda!

歡迎您創建該詞條,闡述對西門子eda的理解,并與今后在此搜索西門子eda的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473