5nm 工藝 文章 最新資訊

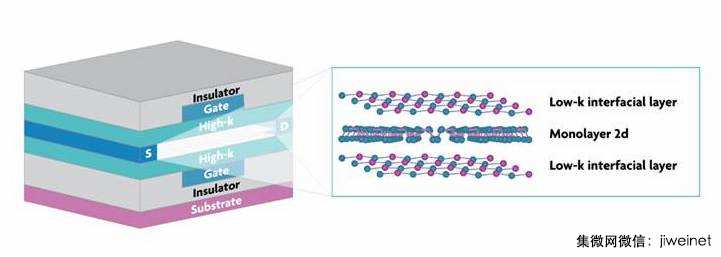

Imec:下一代 5nm 2D材料可望突破摩爾定律限制

- 根據(jù)比利時(shí)研究機(jī)構(gòu)Imec指出,設(shè)計(jì)人員可以選擇采用2D非等向性(顆粒狀速度更快)材料(如黑磷單層),讓摩爾定律(Moore‘s Law)擴(kuò)展到超越5納米(nm)節(jié)點(diǎn)。Imec研究人員在Semicon West期間舉辦的年度Imec技術(shù)論壇(Imec Technology Forum)發(fā)表其最新研究成果。 Imec展示的研究計(jì)劃專注于實(shí)現(xiàn)高性能邏輯應(yīng)用的場(chǎng)效電晶體(FET),作為其Core CMOS計(jì)劃的一部份。Imec及其合作伙伴分別在材料、元件與電路層級(jí)實(shí)現(xiàn)協(xié)同最佳化,證實(shí)了在傳

- 關(guān)鍵字: Imec 5nm

下一代5nm 2D材料可望突破摩爾定律限制?

- Imec 開發(fā)下一代 5nm 2D 通道 FET 架構(gòu),證實(shí)采用 2D 非等向性材料可讓摩爾定律延續(xù)到超越 5nm 節(jié)點(diǎn)… 根據(jù)比利時(shí)研究機(jī)構(gòu)Imec指出,設(shè)計(jì)人員可以選擇采用2D非等向性(顆粒狀速度更快)材料(如黑磷單層),讓摩爾定律(Moore's Law)擴(kuò)展到超越5納米(nm)節(jié)點(diǎn)。Imec研究人員在Semicon West期間舉辦的年度Imec技術(shù)論壇(Imec Technology Forum)發(fā)表其最新研究成果。 Imec開發(fā)的下一代5nm 2D通道

- 關(guān)鍵字: 摩爾定律 5nm

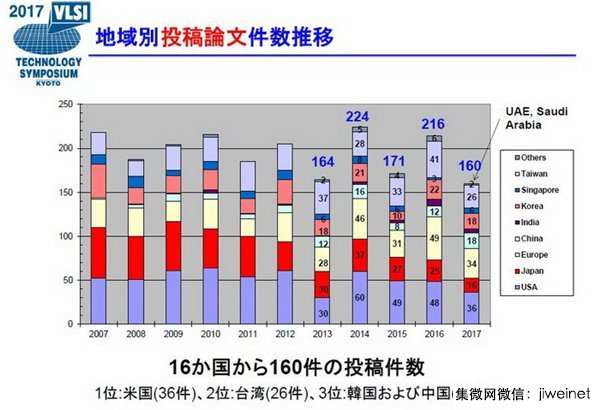

VLSI國(guó)際會(huì)議中國(guó)僅一篇論文入選,占比1/64

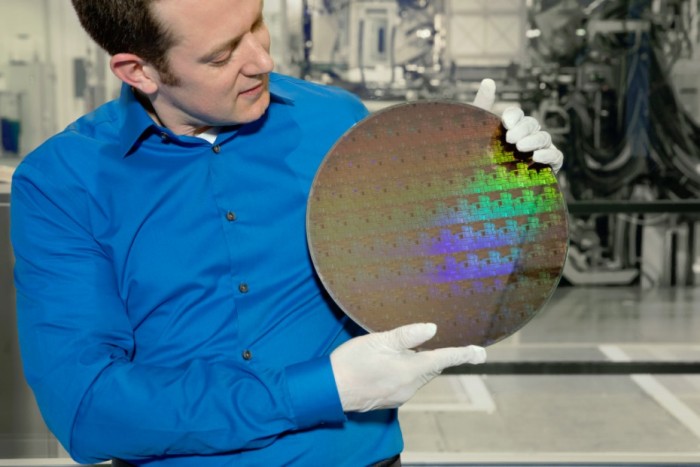

- IBM昨天聯(lián)合三星、Globalfoundries宣布了全球首個(gè)5nm半導(dǎo)體工藝,性能提升40%,功耗降低75%。IBM這則消息就是在VLSI大規(guī)模集成電路會(huì)議上宣布的,這也是國(guó)際級(jí)的半導(dǎo)體會(huì)議。這次會(huì)議也暴露了我們?cè)诎雽?dǎo)體制造技術(shù)依然沒有什么存在感,雖然總計(jì)提交了18篇論文,但入選的只有1篇,僅占全部入選論文的1/64,遠(yuǎn)遠(yuǎn)低于美國(guó)、日本、歐洲、韓國(guó)、新加坡及臺(tái)灣地區(qū)。 2017年的VLSI國(guó)際會(huì)議是在日本東京舉行的,昨天正式開幕,會(huì)期8天,全球領(lǐng)先的半導(dǎo)體技術(shù)公司、科研機(jī)構(gòu)匯聚一堂討論未來技

- 關(guān)鍵字: VLSI 工藝

IBM和三星推出5nm工藝,為摩爾定律+1s

- 上周,Nvidia CEO黃仁勛在臺(tái)北電腦展上表示摩爾定律已死(黃仁勛說摩爾定律已死,Nvidia要用人工智能應(yīng)對(duì)),不過IBM和三星有不同意見。 雷鋒網(wǎng)消息,日前,IBM聯(lián)合三星宣布了一項(xiàng)名為nanosheets的晶體管制造技術(shù)。該技術(shù)拋棄了標(biāo)準(zhǔn)的 FinFET 架構(gòu),采用全新的四層堆疊納米材料。這項(xiàng)技術(shù)為研發(fā)5nm芯片奠定了基礎(chǔ)。IBM表示,借助該項(xiàng)技術(shù),芯片制造商可以在指甲蓋大小的芯片面積里,塞下將近300億個(gè)晶體管。要知道,高通不久前發(fā)布的采用10nm工藝的旗艦芯片驍龍835,也才不過集

- 關(guān)鍵字: IBM 5nm

IBM三星攜手研發(fā)5nm芯片:成本更低、性能更強(qiáng)

- 據(jù)外媒報(bào)道,三星聯(lián)合 IBM 日前宣布了一項(xiàng)名為 nanosheets 的技術(shù)。得益于該技術(shù),芯片制造商能夠?qū)⒏嗟木w管容納到更小的芯片組里,他們宣稱在 5nm 芯片可以實(shí)現(xiàn)在指甲蓋大小中集成 300 億顆晶體管,而當(dāng)前 10nm 的驍龍 835 僅僅集成的晶體管數(shù)量約為 30 億。 IBM 稱,同樣封裝面積晶體管數(shù)量的增大有非常多的好處,比如降低成本、提高性能,而且非常重要的一點(diǎn)是,5nm 加持下,現(xiàn)有設(shè)備如手機(jī)的電池壽命將提高 2 至 3 倍。早在 2015 年,IBM 就攜手 Glo

- 關(guān)鍵字: IBM 5nm

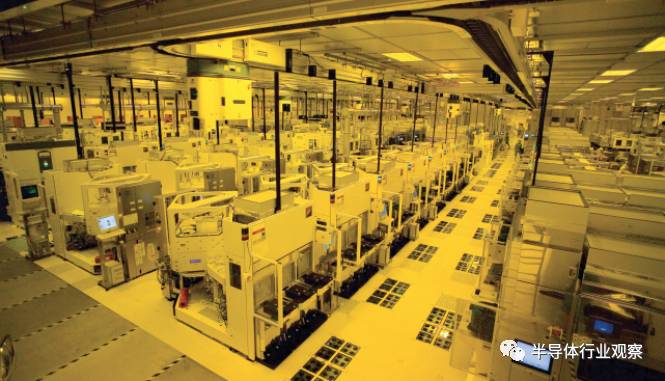

專項(xiàng)助力填補(bǔ)產(chǎn)業(yè)鏈空白 集成電路制造產(chǎn)業(yè)生態(tài)日益完善

- 如今,濃縮在小小芯片上的集成電路成為社會(huì)發(fā)展的重要支撐。電腦、手機(jī)、家電、汽車、機(jī)器人等各種產(chǎn)品都離不開集成電路。沒有集成電路產(chǎn)業(yè)的支撐,信息社會(huì)就失去了根基,集成電路因此被喻為現(xiàn)代工業(yè)的“糧食”。 我國(guó)作為全球最大的半導(dǎo)體市場(chǎng),對(duì)集成電路產(chǎn)品的需求持續(xù)快速增長(zhǎng)。長(zhǎng)期以來,發(fā)達(dá)國(guó)家對(duì)出口到中國(guó)的制造裝備、材料以及工藝技術(shù)進(jìn)行嚴(yán)格審查和限制。想要擁有自主知識(shí)產(chǎn)權(quán)的高技術(shù)芯片,就必須發(fā)展我國(guó)自己的集成電路產(chǎn)業(yè)體系。 2008年,“極大規(guī)模集成電路制造裝備及成

- 關(guān)鍵字: 集成電路 工藝

臺(tái)積電2019年上半年試產(chǎn)5nm制程

- 晶圓代工龍頭臺(tái)積電年度股東常會(huì)將于6月8日登場(chǎng),并于今(24)日上傳致股東報(bào)告書,當(dāng)中揭露先進(jìn)制程技術(shù)最新進(jìn)展,其中,7納米已在今年4月開始試產(chǎn),預(yù)期良率改善將相當(dāng)快速,5納米則維持原先計(jì)劃,預(yù)計(jì)2019年上半年試產(chǎn)。 臺(tái)積電董事長(zhǎng)張忠謀指出,去年間與主要客戶及硅智財(cái)供應(yīng)商攜手合作完成7納米技術(shù)硅智財(cái)設(shè)計(jì),并開始進(jìn)行硅晶驗(yàn)證,按照計(jì)劃在今年4月試產(chǎn)。 5納米部分,張忠謀表示,規(guī)劃使用極紫外光(EUV)微影技術(shù),以降低制程復(fù)雜度,制程技術(shù)預(yù)計(jì)2019年上半年試產(chǎn)。 10納米部分則是已在

- 關(guān)鍵字: 臺(tái)積電 5nm

臺(tái)積電5nm 估2019年完成技術(shù)驗(yàn)證

- 臺(tái)積電物聯(lián)網(wǎng)業(yè)務(wù)開發(fā)處資深處長(zhǎng)王耀東表示,未來臺(tái)積電成長(zhǎng)動(dòng)能來自于高階智慧型手機(jī)、高效運(yùn)算晶片、物聯(lián)網(wǎng)及車用電子。而臺(tái)積電在10奈米技術(shù)開發(fā)如預(yù)期,今年底可以進(jìn)入量產(chǎn),第一個(gè)采用10奈米產(chǎn)品已達(dá)到滿意良率,目前已經(jīng)有三個(gè)客戶產(chǎn)品完成設(shè)計(jì)定案,預(yù)期今年底前還有更多客戶會(huì)完成設(shè)計(jì)定案,該產(chǎn)品在明年第1季開始貢獻(xiàn)營(yíng)收,且在2017年快速提升量產(chǎn)。 7奈米部分,臺(tái)積電該部分進(jìn)度優(yōu)異,7奈米在PPA及進(jìn)展時(shí)程均領(lǐng)先競(jìng)爭(zhēng)對(duì)手,兩個(gè)應(yīng)用平臺(tái)高階智慧型手機(jī)及高效運(yùn)算晶片客戶都積極采用臺(tái)積電7奈米先進(jìn)制程技術(shù),且

- 關(guān)鍵字: 臺(tái)積電 5nm

【IITC/AMC 2016】5nm工藝IC布線技術(shù)發(fā)展方向明確

- 由IEEEElectronDeviceSociety主辦的半導(dǎo)體互連(布線)技術(shù)相關(guān)國(guó)際會(huì)議“IEEEInternationalInterconnectTechnologyConference(IITC)2016”于5月23~26日在美國(guó)圣荷西舉辦。這是該會(huì)議時(shí)隔兩年再次回到美國(guó),共有超過230人參加,展開了積極的討論。 IITC2016的論文數(shù)量為一般口頭演講(包括主題演講)45件,展板發(fā)表33件。一般演講按領(lǐng)域劃分,涵蓋硅化物的“MUP(Materials

- 關(guān)鍵字: 5nm 布線技

英特爾第三款10nm CPU架構(gòu)曝光 5nm芯片2022年推出

.jpg)

- The Motley Fool談?wù)摿擞⑻貭栍?jì)劃推出的三個(gè)10nm節(jié)點(diǎn)架構(gòu),而不是此前預(yù)期的兩種:“管理層向投資者表示,他們正試圖回到2年/低于10nm的節(jié)奏(此話或意味著2年內(nèi)從10nm轉(zhuǎn)到7nm)。不過根據(jù)剛從熟知英特爾計(jì)劃的消息人士那獲得的信息,該公司正致力于三款、而不是兩款10nm節(jié)點(diǎn)架構(gòu)”。 此前有消息稱,Kaby Lake會(huì)停留在當(dāng)前的14nm節(jié)點(diǎn),并打亂英特爾每2年一升級(jí)的制造技術(shù)步伐。該公司首款10nm處理器架構(gòu)被稱作“Cannonlake&rd

- 關(guān)鍵字: 英特爾 5nm

10nm跨三世代 Intel 2020年進(jìn)5nm制程

- 先前證實(shí)采用10nm制程技術(shù)的“Cannonlake”將延后至2017年下半年間推出消息后,相關(guān)消息具體透露Intel計(jì)畫將以10nm制程打造代 號(hào)“Icelake”與“Tigerlake”處理器系列,分別將于2018年與2019年揭曉,同時(shí)預(yù)計(jì)在2020年時(shí)進(jìn)入5nm制程發(fā)展,但目前暫時(shí) 尚未透露預(yù)計(jì)推行處理器代號(hào)名稱。 根 據(jù)overclock3d.net網(wǎng)站取得資料顯示,Intel將以10nm制程技術(shù)打造代號(hào)&ldqu

- 關(guān)鍵字: Intel 5nm

5nm 工藝介紹

您好,目前還沒有人創(chuàng)建詞條5nm 工藝!

歡迎您創(chuàng)建該詞條,闡述對(duì)5nm 工藝的理解,并與今后在此搜索5nm 工藝的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)5nm 工藝的理解,并與今后在此搜索5nm 工藝的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司