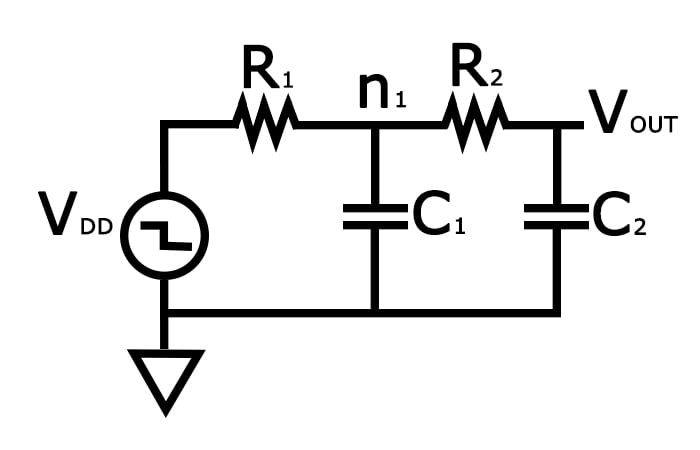

在超大規模集成電路(VLSI)設計中,時鐘域交叉過程必然會出現亞穩態現象。要實現魯棒且高可靠性的電路設計,必須對亞穩態進行抑制。想要掌握亞穩態的解決方法,以及如何設計滿足指標要求的同步器,我們需要明確其產生原因、影響因素,以及降低其發生概率的方式。亞穩態與觸發器同步器為了更深入理解時序元件進入亞穩態的過程,以及亞穩態的消解時長,可參考圖 1。圖 1:典型的主從鎖存器觸發器電路圖 1 為典型的主從鎖存器觸發器電路,由主鎖存器和從鎖存器組成,每個鎖存器均包含兩個級聯的反相器。在正常且正確的工作狀態下,時鐘為低

關鍵字:

VLSI 時鐘域交叉 亞穩態 觸發器 同步器

晶圓到晶圓混合鍵合和背面技術的進步將CMOS 2.0從概念變為現實,為計算系統擴展提供了更多選擇。在VLSI 2025 上,imec 研究人員展示了將晶圓間混合鍵合路線圖擴展到250 nm 互連間距的可行性。他們還通過制造120 nm 間距的極小的貫穿介電通孔,在晶圓背面顯示出高度致密的連接。在晶圓兩側建立如此高密度連接的能力為開發基于CMOS 2.0 的計算系統架構提供了一個里程碑,該架構依賴于片上系統內功能層的堆疊。基于CMOS 2.0 的系統還將利用包括供電網絡(BSPDN)在內的后端互連,其優勢可

關鍵字:

202510 晶圓連接 VLSI 2025 imec

SK海力士公司今天宣布,在日本京都舉行的20251年IEEE VLSI研討會上,該公司提出了未來30年的DRAM新技術路線圖和可持續創新的方向。SK海力士首席技術官(CTO)車善勇于6月10日發表了題為“推動DRAM技術創新:邁向可持續未來”的全體會議。首席技術官 Cha 在演講中解釋說,通過當前的技術平臺擴展來提高性能和容量變得越來越困難。“為了克服這些限制,SK海力士將在結構、材料和組件方面進行創新,將4F2 VG(垂直門)平臺和3D DRAM技術應用于10納米級或以下的技術。4F2 VG平臺是下一代

關鍵字:

SK海力士 IEEE VLSI 2025 DRAM

4 月 21 日消息,2025 年超大規模集成電路研討會(VLSI Symposium)定于 2025 年 6 月 8 日至 12 日在日本京都舉行,這是半導體領域的頂級國際會議。VLSI 官方今日發布預覽文檔,簡要介紹了一系列將于 VLSI 研討會上公布的論文,例如 Intel 18A 工藝技術細節。相較于 Intel 3 制程,Intel 18A 節點在性能、能耗及面積(PPA)指標上均實現顯著提升,將為消費級客戶端產品與數據中心產品帶來實質性提升。英特爾聲稱,在相同電壓(1.1V)和復雜度條件下,I

關鍵字:

英特爾 2025 VLSI 18A 制程技術

眾所周知,為了使晶體管更小,人們做了大量工作。然而,仍然需要對 VLSI 電路和模塊進行相應的工作,以適應更小的設計。這些 VLSI 電路和模塊可能很簡單,只有幾個邏輯門(包含兩到四個晶體管),也可能是包含成千上萬個晶體管的更大系統。相反,這些系統需要滿足各種工作條件下的速度/延遲和功率要求。眾所周知,為了使晶體管更小,人們做了大量工作。然而,仍然需要對 VLSI 電路和模塊進行相應的工作,以適應更小的設計。這些 VLSI 電路和模塊可能很簡單,只有幾個邏輯門(包含兩到四個晶體管),也可能是包含成千上萬個

關鍵字:

VLSI

IT之家 11 月 20 日消息,相對于 IEEE 國際研討會,在半導體和集成電路領域還有著三大盛會的存在,他們分別是:ISSCC(International Solid-State Circuits Conference,國際固態電路會議)、IEDM(International Electron Devices Meeting,國際電子器件會議)、VLSI(Symposium on VLSI Technology and Circuits,超大規模集成電路技術和電路研討會)。這三大會議,并稱集

關鍵字:

ISSCC IEDM VLSI IEEE

引 言JPEG 2000是為了彌補JPEG的不足而提出的新一代靜止圖像壓縮國際標準。其目標是對多種類型的靜止圖像實現高效壓縮,并要求壓縮碼流具有較好

關鍵字:

JPEG 2000 VLSI 標準

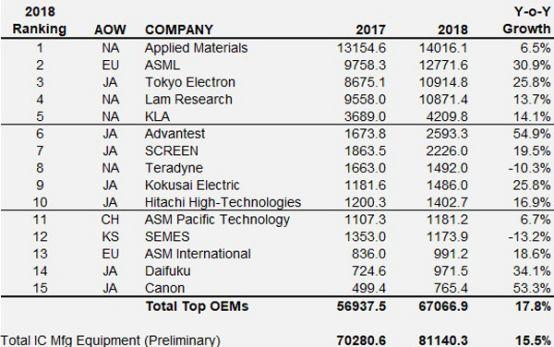

中微半導體設備(上海)有限公司(以下簡稱“中微”)宣布,中微在VLSIresearch(美國領先的半導體行業市場研究公司,以下簡稱“VLSI”)舉辦的2018年度客戶滿意度調查(簡稱“CSS”)中榮登上榜,在多項排名中位居前列。VLSI從1988年開始每年都會舉辦這項客戶滿意度調查,這是業內唯一一項能讓不同地區的客戶對它們全球的半導體設備和子系統的供應商進行匿名反饋的調查。上榜企業名單中有來自美國、歐洲、亞洲和以色列的企業,中微是其中唯一一家中國本土的半導體設備公司。 中微在芯片制造設備專業型供應商

關鍵字:

中微,VLSI

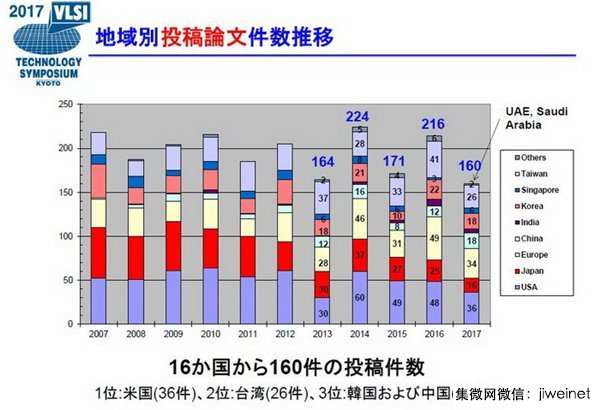

IBM昨天聯合三星、Globalfoundries宣布了全球首個5nm半導體工藝,性能提升40%,功耗降低75%。IBM這則消息就是在VLSI大規模集成電路會議上宣布的,這也是國際級的半導體會議。這次會議也暴露了我們在半導體制造技術依然沒有什么存在感,雖然總計提交了18篇論文,但入選的只有1篇,僅占全部入選論文的1/64,遠遠低于美國、日本、歐洲、韓國、新加坡及臺灣地區。

2017年的VLSI國際會議是在日本東京舉行的,昨天正式開幕,會期8天,全球領先的半導體技術公司、科研機構匯聚一堂討論未來技

關鍵字:

VLSI 工藝

正電子發射斷層成像系統(PET)前端讀出電路是數模混合信號超大規模集成電路芯片.針對多通道高性能PET專用集成電路芯片的特點,采用JTAG控制器對該芯片進行初始控制和輔助測試.采用TSMC 0.18μmCMOS工藝設計實現了一個可擴展的JTAG控制器IP核,支持14組可擴展控制信號和16個多位寄存器掃描鏈的讀/寫操作,并配備定制的底層驅動

關鍵字:

VLSI JTAG PET成像系統

近年來,鋰離子電池以其能量密度高、自放電率低、單節電池電壓高等優點,獲得了廣泛應用,相應的電池管理芯片研究也在不斷地完善與發展。其中,為了盡可能保證電池使用的安全性并且延長電池的使用壽命,電池管理芯片的功能及低功耗研究顯得更為迫切和必要。

關鍵字:

混合信號電路 VLSI RTL編碼

近年來,鋰離子電池以其能量密度高、自放電率低、單節電池電壓高等優點,獲得了廣泛應用,相應的電池管理芯片研究也在不斷地完善與發展。其中,為了盡可能保證電池使用的安全性并且延長電池的使用壽命,電池管理芯片的功能及低功耗研究顯得更為迫切和必要。

關鍵字:

鋰離子電池管理芯片 Top-Down低功耗設計 VLSI

SOC技術是當前大規模集成電路(VLSI)的發展趨勢,也是世紀集成電路技術的主流,其為集成電路產業和集成電路應用技術提供了前所未有的廣闊市場和難得的發展機遇。SOC為微電子應用產品研究、開發和生產提供了新型的優秀的技術方法和工具,也是解決電子產品開發中的及時上市(TTM——Time to Market)的主要技術與方法。

關鍵字:

SoC 集成開發環境 VLSI 嵌入式系統 處理器

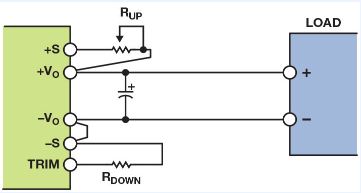

最近,超大規模集成(VLSI)技術的發展擴寬了數字控制應用范圍,尤其是在電源電子元件方面的應用。數字控制IC具有多種優勢,比如裸片尺寸更小、無源元件數量更少、成本更低。 另外,數字控制可利用電源管理總線(PMBus)來完成系統配置;高級控制算法能改善性能;可編程性則可實現應用優化。 隨著數字電源管理的進一步普及并代替大量模擬控制器,它必須保持現有功能的向后兼容性,從而使數字電源模塊和模擬電源模塊均可在同一個系統中工作。 模擬電源模塊中一般使用輸出電壓調整,這樣最終用戶可以通過外部電阻更改

關鍵字:

數字電源控制器 VLSI

vlsi介紹

SSI 小規模集成電路(Small Scale Integrated circuites),MSI 中規模集成電路(Medium Scale Integrated circuites), LSI 大規模集成電路(Large Scale Integrated circuites),VLSI 超大規模集成電路(Very Large Scale Integrated circuites),ULSI [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473