asic ip 文章 最新資訊

芯原與谷歌聯(lián)合推出開源Coral NPU IP

- 芯原股份(芯原)近日宣布與谷歌聯(lián)合推出面向始終在線、超低能耗端側(cè)大語言模型應(yīng)用的Coral NPU IP。該IP基于谷歌在開放機(jī)器學(xué)習(xí)編譯器方面的基礎(chǔ)研究成果,并結(jié)合AI的安全特性進(jìn)行了強(qiáng)化,為開發(fā)者提供統(tǒng)一的開源技術(shù)平臺,以構(gòu)建強(qiáng)大的邊緣AI生態(tài)系統(tǒng)。Coral NPU基于RISC-V開放指令集架構(gòu)標(biāo)準(zhǔn)構(gòu)建,引入原生張量處理能力,支持主流機(jī)器學(xué)習(xí)框架,如JAX、PyTorch和TensorFlow Lite(TFLite),并采用基于開放標(biāo)準(zhǔn)的工具,例如來自低級虛擬機(jī)(LLVM)項(xiàng)目的多級中間表示(ML

- 關(guān)鍵字: 芯原 谷歌 開源Coral NPU IP Coral NPU

非云端AI芯片淡旺季節(jié)奏大亂 顯示驅(qū)動(dòng)IC設(shè)計(jì)加速靠攏ASIC

- 近日臺系顯示驅(qū)動(dòng)芯片(DDI IC)業(yè)者陸續(xù)公布最新財(cái)報(bào)表現(xiàn)和未來展望,有鑒于中國消費(fèi)市場因?yàn)橄惹暗难a(bǔ)貼政策已經(jīng)提前實(shí)現(xiàn)換機(jī)需求,加上美國關(guān)稅政策讓供應(yīng)鏈也決定提前拉貨,2025年下半幾乎都呈現(xiàn)旺季不旺,更可以說是「全年淡旺季節(jié)奏直接逆轉(zhuǎn)」。如此淡旺季節(jié)奏混亂的情況,芯片業(yè)者坦言,預(yù)估到2026年都還有可能重演。 聯(lián)詠、奇景光電、天鈺等臺系驅(qū)動(dòng)IC設(shè)計(jì)業(yè)者的多元布局策略,已經(jīng)快速開展,而這樣的尷尬難題,也普遍出現(xiàn)在「非云端AI」的晶片業(yè)者身上。IC供應(yīng)鏈業(yè)者表示,而面臨到DDI IC整體需求轉(zhuǎn)弱,且出貨表

- 關(guān)鍵字: AI芯片 顯示驅(qū)動(dòng) IC設(shè)計(jì) ASIC

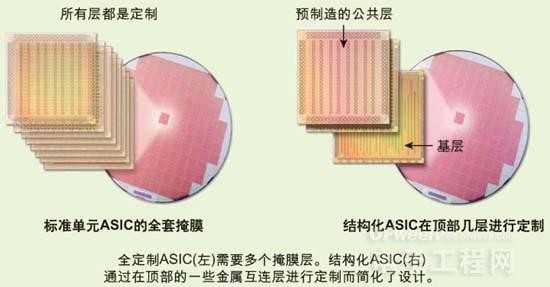

英特爾將在利潤豐厚的ASIC業(yè)務(wù)中與博通和Marvell競爭

- 關(guān)于ASIC 業(yè)務(wù),Lip-Bu Tan 在最近一次投資者電話會(huì)議上關(guān)于新英特爾中央工程集團(tuán)以及 ASIC 和設(shè)計(jì)服務(wù)業(yè)務(wù)的準(zhǔn)備好的聲明中所說的內(nèi)容。專用集成電路是專為特定應(yīng)用而設(shè)計(jì)的定制設(shè)計(jì)的半導(dǎo)體,與 CPU 或 GPU 等通用芯片相比,可提供無與倫比的性能、能效和成本效益。ASIC 在人工智能、高性能計(jì)算、電信、汽車和消費(fèi)電子等大批量市場中至關(guān)重要。與可編程設(shè)備不同,ASIC 針對特定任務(wù)進(jìn)行了優(yōu)化,可實(shí)現(xiàn)人工智能加速器、5G/6G 基礎(chǔ)設(shè)施和邊緣計(jì)算等創(chuàng)新。ASIC 生態(tài)系統(tǒng)在無晶圓廠設(shè)計(jì)公司、代

- 關(guān)鍵字: 英特爾 ASIC 博通 Marvell

無懼ASIC毛利率加速下滑 IC設(shè)計(jì)搶單仍拚「唯快不破」

- 云端AI特用芯片(ASIC)需求節(jié)節(jié)攀升,各界對其潛在市場的規(guī)模,預(yù)估數(shù)字也是愈來愈大。 近期聯(lián)發(fā)科在法說會(huì)上,也將整塊市場從原先預(yù)估的400億美元,上修到500億美元,前景值得期待。不過也因更多不同背景的相關(guān)業(yè)者加入ASIC市場,競爭激烈程度不可同日而語,加上部分大客戶已經(jīng)開始可以自己更多的設(shè)計(jì)工作,這導(dǎo)致「項(xiàng)目定價(jià)權(quán)」愈來愈倒向客戶一端。 IC設(shè)計(jì)人士坦言,ASIC業(yè)務(wù)的整體毛利率空間,近期有加速下滑趨勢,盡管如此,爭取唯快不破、搶下訂單的業(yè)者不在少數(shù)。 晶片業(yè)者坦言,其實(shí)ASIC

- 關(guān)鍵字: ASIC IC設(shè)計(jì)

CAST通過新的Catalyst 計(jì)劃簡化RISC-V嵌入式處理器 IP 的采用

- 半導(dǎo)體 IP 提供商 CAST, Inc. 于 2025 年 10 月 22 日在加利福尼亞州圣克拉拉舉行的 RISC-V 峰會(huì)上推出了其催化劑?計(jì)劃,旨在加速將開源處理器架構(gòu)集成到資源受限的設(shè)備中。該計(jì)劃解決了嵌入式系統(tǒng)開發(fā)人員的一個(gè)持續(xù)痛點(diǎn):RISC-V 處理器的壓倒性可配置性。通過提供預(yù)先調(diào)整的、可立即部署的 IP 核以及靈活的許可和專家支持,CAST 旨在消除復(fù)雜性,從而在物聯(lián)網(wǎng)傳感器、可穿戴設(shè)備和工業(yè)控制器等低功耗、成本敏感的應(yīng)用中實(shí)現(xiàn)更快的原型設(shè)計(jì)和部署。RISC-V 是一種免版稅指令集架構(gòu),

- 關(guān)鍵字: CAST Catalyst RISC-V 嵌入式處理器 IP

用于改進(jìn)設(shè)計(jì)驗(yàn)證的斷言 IP (AIP)

- 多年來,設(shè)計(jì)重用方法為半導(dǎo)體 IP (SIP) 創(chuàng)造了一個(gè)市場,現(xiàn)在有了正式的技術(shù),就需要斷言 IP (AIP)。其中,每個(gè)AIP都是硬件設(shè)計(jì)中用于檢測被測設(shè)計(jì)(DUT)中的協(xié)議和功能違規(guī)的可重用和可配置驗(yàn)證組件。LUBIS EDA 專注于正式服務(wù)和工具,因此我收到了有關(guān)他們開發(fā)這些 AIP 和檢測高風(fēng)險(xiǎn) IP 中極端情況錯(cuò)誤的方法的最新信息。在詳細(xì)介紹 LUBIS EDA 使用的方法之前,讓我們先回顧一下基于仿真的驗(yàn)證與形式驗(yàn)證有何不同。通過仿真,工程師正在編寫激勵(lì)來覆蓋設(shè)計(jì)的所有已知狀態(tài),希望覆蓋范圍

- 關(guān)鍵字: 設(shè)計(jì)驗(yàn)證 斷言 IP AIP

應(yīng)對團(tuán)體設(shè)計(jì)項(xiàng)目的挑戰(zhàn)

- 世界各地的政府和行業(yè)齊心協(xié)力解決大規(guī)模芯片設(shè)計(jì)挑戰(zhàn)。美國國防部的微電子中心 (ME Commons)、歐盟芯片法案試點(diǎn)線和日本政府支持的 Rapidus 財(cái)團(tuán)等團(tuán)體通常由老牌公司、研究機(jī)構(gòu)、學(xué)術(shù)界和初創(chuàng)公司組成——每個(gè)機(jī)構(gòu)都帶來了不同的技能。是德科技設(shè)計(jì)與驗(yàn)證業(yè)務(wù)部總經(jīng)理 Nilesh Kamdar 表示,在這種情況下,芯片設(shè)計(jì)界正在加速、擴(kuò)大規(guī)模,并承擔(dān)如果沒有政府資助,他們可能不會(huì)承擔(dān)的風(fēng)險(xiǎn),是德科技參與了國防部的許多 ME Commons,最近與 Rapidus 合作開發(fā)了高精度工藝設(shè)計(jì)套

- 關(guān)鍵字: 團(tuán)體設(shè)計(jì)項(xiàng)目 IP 是德科技

無縫升級嵌入式芯片AI能力!安謀科技Arm China推出新一代CPU IP“星辰”STAR-MC3

- 國內(nèi)領(lǐng)先的芯片IP設(shè)計(jì)與服務(wù)提供商安謀科技(中國)有限公司(以下簡稱“安謀科技”)今日宣布,正式推出自主研發(fā)的第三代高能效嵌入式芯片IP——“星辰”STAR-MC3。該產(chǎn)品基于Arm?v8.1-M架構(gòu),向前兼容傳統(tǒng)MCU架構(gòu),集成Arm Helium?技術(shù),顯著提升CPU在AI計(jì)算方面的性能,同時(shí)兼具優(yōu)異的面效比與能效比,實(shí)現(xiàn)高性能與低功耗設(shè)計(jì),面向AIoT智能物聯(lián)網(wǎng)領(lǐng)域,為主控芯片及協(xié)處理器提供核芯架構(gòu),助力客戶高效部署端側(cè)AI應(yīng)用。STAR-MC3處理器概覽STAR-MC3五大技術(shù)亮點(diǎn)1.更強(qiáng)的AI能

- 關(guān)鍵字: 安謀科技 Arm China CPU IP 嵌入式芯片

SiFive推出全新RISC-V IP,融合標(biāo)量、向量與矩陣運(yùn)算

- SiFive 近日正式推出第二代 Intelligence? 系列,進(jìn)一步強(qiáng)化其在 RISC-V AI IP 領(lǐng)域的技術(shù)領(lǐng)先優(yōu)勢。此次發(fā)布的五款新產(chǎn)品,專為加速數(shù)千種 AI 應(yīng)用場景中的工作負(fù)載而設(shè)計(jì)。該系列包括兩款全新產(chǎn)品——X160 Gen 2 與 X180 Gen 2,以及升級版 X280 Gen 2、X390 Gen 2 和 XM Gen 2。所有新產(chǎn)品均具備增強(qiáng)的標(biāo)量、向量處理能力,其中 XM 產(chǎn)品還加入了矩陣處理功能,專為現(xiàn)代AI工作負(fù)載設(shè)計(jì)。其中,X160 Gen 2 與 X180 Gen

- 關(guān)鍵字: SiFive RISC-V IP

博通據(jù)報(bào)道增加 2026 年 CoWoS 訂單,因 ASIC 需求強(qiáng)勁

- 隨著英偉達(dá)最新財(cái)報(bào)凸顯人工智能基礎(chǔ)設(shè)施的繁榮,投資者的關(guān)注點(diǎn)也轉(zhuǎn)向了專用集成電路的需求。據(jù)商業(yè)時(shí)報(bào)報(bào)道,博通已增加明年 CoWoS 封裝的訂單,這一舉動(dòng)可能是由谷歌、Meta 和其他云巨頭不斷增長的定制芯片需求推動(dòng)的。正如商業(yè)時(shí)報(bào)所暗示的,晶圓代工廠已經(jīng)開始尋求 2026 年的預(yù)測,博通已提高該年 CoWoS 封裝的訂單。6 月,?路透社報(bào)道,美國芯片制造商對第三季度的收入預(yù)期約為 158 億美元,這得益于網(wǎng)絡(luò)設(shè)備和定制人工智能芯片的強(qiáng)勁需求。博通,正如路透社所強(qiáng)調(diào)的,為人工智能和云服務(wù)提供商如

- 關(guān)鍵字: ASIC CoWos 博通

ASIC市場龍頭廠先搶先贏 第二梯隊(duì)營收進(jìn)帳恐等2028年

- NVIDIA在云端AI GPU運(yùn)算占據(jù)絕對的領(lǐng)先地位,但是,特用芯片(ASIC)需求在未來幾年持續(xù)火熱,是市場的絕對共識,透過各種方式投入到這塊市場的芯片業(yè)者也愈來愈多,第一梯隊(duì)包括聯(lián)發(fā)科、博通(Broadcom)、Marvell、世芯等。 然而,IC設(shè)計(jì)業(yè)者坦言,后進(jìn)的第二梯隊(duì),似乎就沒那么容易有立即的營收貢獻(xiàn)了。熟悉ASIC市場人士評估,現(xiàn)在大家看得到的一些領(lǐng)先集團(tuán),無論是耕耘市場比較久的老牌ASIC業(yè)者世芯,還是跨足ASIC戰(zhàn)果豐碩的博通、Marvell,甚或是2020年之后才加速SerDes技術(shù)I

- 關(guān)鍵字: ASIC 博通 Marvell

燦芯半導(dǎo)體推出PCIe 4.0 PHY IP

- 一站式定制芯片及IP供應(yīng)商——燦芯半導(dǎo)體(上海)股份有限公司(燦芯股份,688691)宣布推出基于28HKC+ 0.9V/1.8V平臺的PCIe 4.0 PHY IP。該P(yáng)HY IP符合PCIe 4.0規(guī)范的要求,支持PIPE 4.4.1/5.2接口及2.5Gbps至16Gbps的數(shù)據(jù)傳輸速率,全面覆蓋PCIe Gen4.0/3.0/2.0/1.0標(biāo)準(zhǔn),并兼容Rapid IO、JESD204B/C、USB3.2/3.1/3.0、10GBASE-R/KR等其他協(xié)議。憑借其優(yōu)越的

- 關(guān)鍵字: 燦芯 PCIe 4.0 PHY IP

Ceva無線連接IP市場份額達(dá)68%,穩(wěn)居行業(yè)首位

- 據(jù)IPnest最新發(fā)布的2025年設(shè)計(jì)IP報(bào)告顯示,Ceva公司在無線連接IP領(lǐng)域繼續(xù)保持領(lǐng)先地位,市場份額在2024年增長至68%。這一數(shù)字是其最接近競爭對手的10倍以上,進(jìn)一步鞏固了其在智能邊緣設(shè)備聯(lián)機(jī)功能中的核心地位。Ceva(納斯達(dá)克股票代碼:CEVA)作為全球領(lǐng)先的智能邊緣領(lǐng)域半導(dǎo)體產(chǎn)品和軟件IP授權(quán)許可廠商,其技術(shù)覆蓋藍(lán)牙、Wi-Fi、UWB、802.15.4及蜂窩物聯(lián)網(wǎng)IP解決方案。這些技術(shù)為下一代智能邊緣設(shè)備提供了重要支持,滿足了市場對高性能、低功耗解決方案的不斷增長需求。Ceva首席運(yùn)營

- 關(guān)鍵字: Ceva 無線連接 IP

Arteris將為AMD新一代AI芯粒設(shè)計(jì)提供FlexGen智能片上網(wǎng)絡(luò) (NoC) IP

- 在AI計(jì)算需求重塑半導(dǎo)體市場的背景下。致力于加速系統(tǒng)級芯片 (SoC) 開發(fā)的領(lǐng)先系統(tǒng) IP 提供商 Arteris 公司近日宣布,高性能與自適應(yīng)計(jì)算領(lǐng)域的全球領(lǐng)導(dǎo)者 AMD(納斯達(dá)克股票代碼:AMD)已在其新一代AI 芯粒設(shè)計(jì)中采用FlexGen片上網(wǎng)絡(luò)互連IP。Arteris的這項(xiàng)智能NoC IP技術(shù)將為 AMD 芯粒提供高性能數(shù)據(jù)傳輸支持,賦能AMD從數(shù)據(jù)中心到邊緣及終端設(shè)備的廣泛產(chǎn)品組合中的AI應(yīng)用。Arteris FlexGen NoC IP與AMD Infinity Fabric?互連技術(shù)的戰(zhàn)

- 關(guān)鍵字: Arteris AMD AI芯粒 片上網(wǎng)絡(luò) NoC IP

四大核心要素驅(qū)動(dòng)汽車智能化創(chuàng)新與相關(guān)芯片競爭格局

- 智能汽車時(shí)代的加速到來,使車載智能系統(tǒng)面臨前所未有的算力需求。隨著越來越多車型引入電子電氣架構(gòu)轉(zhuǎn)向中心化、智能駕駛的多傳感器融合、智能座艙的多模態(tài)交互以及生成式AI驅(qū)動(dòng)的虛擬助手等創(chuàng)新技術(shù),都要求車用主芯片能夠同時(shí)勝任圖形渲染、AI推理和安全計(jì)算等多重任務(wù)。當(dāng)下,功能安全、高效高靈活性的算力、產(chǎn)品生命周期,以及軟件生態(tài)兼容性這“四大核心要素”,已成為衡量智能汽車AI芯片創(chuàng)新力和市場競爭力的核心標(biāo)準(zhǔn)。傳統(tǒng)汽車計(jì)算架構(gòu)中,往往采用CPU與GPU或/和NPU等計(jì)算單元組成異構(gòu)計(jì)算模式;隨著自動(dòng)駕駛算法從L1向L

- 關(guān)鍵字: 202507 汽車智能化 Imagination GPU IP

asic ip介紹

您好,目前還沒有人創(chuàng)建詞條asic ip!

歡迎您創(chuàng)建該詞條,闡述對asic ip的理解,并與今后在此搜索asic ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對asic ip的理解,并與今后在此搜索asic ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司