dsp+fpga 文章 最新資訊

32位DSP兩級cache的結(jié)構(gòu)設(shè)計

- 采用自頂向下的流程設(shè)計了一款32位DSP的cache。該cache采用兩級結(jié)構(gòu),第一級采用哈佛結(jié)構(gòu),第二級采用普林斯頓結(jié)構(gòu)。本文詳細論述了該cache的結(jié)構(gòu)設(shè)計及采用的算法。

- 關(guān)鍵字: 結(jié)構(gòu)設(shè)計 cache 兩級 DSP 32位

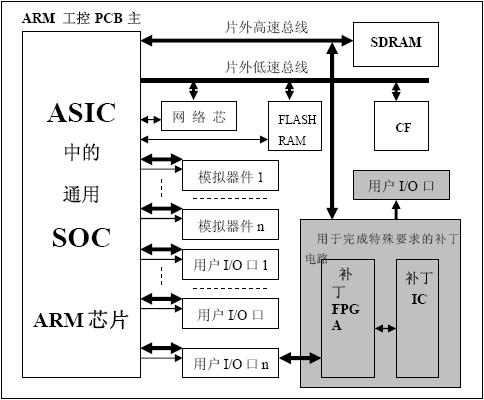

全新片上可編程系統(tǒng)(SOPC)多參監(jiān)護儀專用主控板簡介

- 多參監(jiān)護儀主控板是多參監(jiān)護儀執(zhí)行信息處理的核心部件,主要解決臨床生理信息的傳輸、存儲、顯示、交換和信息數(shù)據(jù)的組合加工。特別是數(shù)字化醫(yī)院的發(fā)展,HIS、CIS 系統(tǒng)的建立和普遍使用,使得多參監(jiān)護儀不僅是一個生理參數(shù)的顯示和記錄終端,而且正成為醫(yī)療單位信息系統(tǒng)中必不可少的一個重要的臨床、生理信息平臺。它的許多技術(shù)指標直接體現(xiàn)了多參監(jiān)護儀整機的重要技術(shù)性能指標。在多參監(jiān)護儀市場競爭日趨激烈的今天,選擇一款技術(shù)既先進,性能價格比又高的主控板,無疑可以大大提高它的市場競爭力。 一、目前國內(nèi)多參監(jiān)護儀主控板

- 關(guān)鍵字: SOPC 主控板 監(jiān)護儀 ARM IP FPGA

基于FPGA的通用開關(guān)電源控制器硬件模擬開發(fā)平臺的

- 設(shè)計了一套基于FPGA的通用離線開關(guān)電源硬件模擬開發(fā)平臺,并對此硬件開發(fā)平臺的硬件組成及工作原理進行了分析。利用此硬件開發(fā)平臺對開關(guān)電源控制器進行硬件模擬,可以彌補控制芯片設(shè)計過程中軟件仿真的不足,大大縮短控制芯片開發(fā)周期。

- 關(guān)鍵字: FPGA 通用開關(guān)電源 控制器 開發(fā)平臺

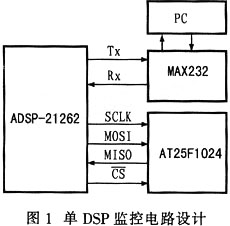

ADSP-21262型DSP的監(jiān)控設(shè)計

- 1 引言 隨著數(shù)字信號處理理論的日趨完善和超大規(guī)模集成電路技術(shù)的飛速發(fā)展,在各種實時處理應(yīng)用需求的推動下,數(shù)字信號處理器(DSP)也得到了越來越廣泛的應(yīng)用。 DSP的監(jiān)控是DSP開發(fā)和應(yīng)用中十分重要的環(huán)節(jié)。目前在DSP的開發(fā)過程中,最常用的方式是通過購買處理器的JTAG仿真器和開發(fā)軟件包實現(xiàn)對DSP的調(diào)試和監(jiān)控。JTAG調(diào)試工具的功能十分強大,對于不熟悉DSP內(nèi)部結(jié)構(gòu)和細節(jié)的開發(fā)者而言是一種非常不錯的選擇。但是此種方法也有其缺陷:首先,開發(fā)成本比較昂貴,一般購買正版仿真器和軟件包的價格都在

- 關(guān)鍵字: DSP 監(jiān)控 JTAG PC

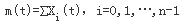

基于DSP的音頻會議信號合成算法研究

- 隨著在數(shù)字信號處理(DSP)算法和芯片處理能力以及通信網(wǎng)絡(luò)結(jié)構(gòu)優(yōu)化等方面的不斷發(fā)展,現(xiàn)代化通信已經(jīng)迅速普及。音頻會議是眾多通信系統(tǒng)的必備功能。有多個用戶參與的音頻會議,最簡單的模式可以使用令牌控制下的互斥模式,使只有擁有發(fā)言權(quán)的那個與會者才可以講話。在這種模式下,每個與會者某一時刻只能聽到一路音頻信號,這種“半雙工”模式對于音頻會議是不方便和不實際的。 真正的電話會議應(yīng)當仿真多個與會者在一個會議室進行對話的情形。但是由于與會終端在物理上并不在一起,而每個終端只有一套音頻輸

- 關(guān)鍵字: DSP 音頻會議 音頻輸出 ITU-T 有無聲檢測

視頻監(jiān)控系統(tǒng)中ARM與DSP的HPI接口設(shè)計

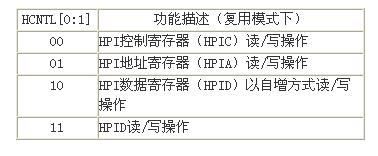

- 1 引言 隨著網(wǎng)絡(luò)技術(shù)、圖像處理技術(shù)及嵌入式技術(shù)日趨成熟,視頻監(jiān)控技術(shù)得到廣泛的應(yīng)用。銀行、工廠、政府、學(xué)校等部門,都設(shè)置有監(jiān)控系統(tǒng)。尤其是在國際上一系列恐怖事件后,人們更感到監(jiān)控系統(tǒng)的重要。而且要求視頻監(jiān)控設(shè)備有高清晰的視頻效果的同時,還能對現(xiàn)場進行實時控制。所以,此類設(shè)備不但要有更高的數(shù)據(jù)處理能力和處理精度,還要有強大的系統(tǒng)控制、管理能力以及高速的網(wǎng)絡(luò)數(shù)據(jù)傳輸速率。 目前,市面上主流的視頻監(jiān)控設(shè)備,大致可以分成兩類,一是基于通用微處理器,二是基于數(shù)字信號處理器DSP。兩種芯片在功能上有

- 關(guān)鍵字: ARM DSP HPI 視頻監(jiān)控

NVCM ——PLD便攜應(yīng)用方案的新選擇

- 根據(jù)Semico調(diào)查研究,對于可編程邏輯芯片(PLD而言,便攜式應(yīng)用是一個快速增長的市場,預(yù)估可編程邏輯芯片在這些應(yīng)用領(lǐng)域的市場值將在2010年前超過6億5000萬美元。但是PLD在便攜應(yīng)用中也是優(yōu)缺點都非常明顯的解決方案。PLD提供了相比ASIC和ASSP更加靈活的設(shè)計路徑,通過提供不同的功能設(shè)置,從而設(shè)計出差異化的產(chǎn)品。同時,便攜電子電池供電的局限性,以及在有限空間內(nèi)集成更多功能而又不影響功耗的考慮,都為FPGA帶來了不小的障礙。 當前,PLD市場不乏一些針對便攜應(yīng)用專門優(yōu)化過的方案,例如Xil

- 關(guān)鍵字: NVCM FPGA SiliconBlue Kilopass

CEVA和ARM合作CEVA DSP + ARM多處理器SoC的開發(fā)支持

- 硅產(chǎn)品知識產(chǎn)權(quán) (SIP) 平臺解決方案和數(shù)字信號處理器 (DSP) 內(nèi)核授權(quán)廠商CEVA公司宣布與ARM合作,針對多處理器系統(tǒng)級芯片 (SoC) 解決方案的開發(fā),在ARM? CoreSight? 技術(shù)實現(xiàn)CEVA DSP內(nèi)核的實時跟蹤支持。這種強化的支持將使得日益增多的采用基于CEVA DSP + ARM處理器的SoC客戶,在使用具有ARM Embedded Trace Macrocell? (ETM) 技術(shù)的處理器時,受益于完全的系統(tǒng)可視化,從而簡化調(diào)試過程及確保快

- 關(guān)鍵字: ARM CEVA DSP 多處理器 SoC SIP

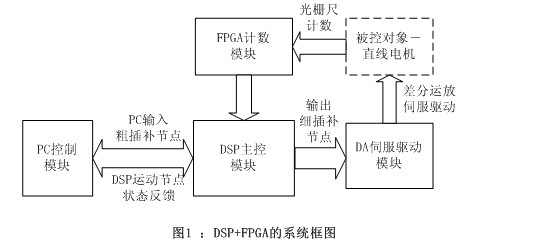

DSP+FPGA在高速高精運動控制器中的應(yīng)用

- 運動控制卡已經(jīng)在數(shù)控機床、工業(yè)機器人、醫(yī)用設(shè)備、繪圖儀、IC電路制造設(shè)備、IC封裝等領(lǐng)域得到了廣泛運用,取得了良好的效果。目前運動控制卡大部分采用8051系列的8位單片機,雖然節(jié)省了開發(fā)周期但缺乏靈活性,難以勝任高要求運作環(huán)境,而且運算能力有限。 DSP的數(shù)據(jù)運算處理功能強大,即使在很復(fù)雜的控制中,采樣周期也可以取得很小,控制效果更接近于連續(xù)系統(tǒng)。把DSP與PC的各自優(yōu)勢結(jié)合將是高性能數(shù)控系統(tǒng)的發(fā)展趨勢。本運動控制器采用TI公司的高性能浮點DSP作為主控芯片,通過ISA接口與PC

- 關(guān)鍵字: DSP FPGA 運動控制 插補 伺服

Altium推出最新版一體化電子產(chǎn)品設(shè)計解決方案

- 日前,Altium 宣布推出擁有 100 多項新特性的最新版一體化電子產(chǎn)品設(shè)計解決方案,從而使截然不同的設(shè)計領(lǐng)域進一步實現(xiàn)了關(guān)聯(lián)融合。 首次實現(xiàn)與機械領(lǐng)域的真正協(xié)作 電子產(chǎn)品通常需要某種形式的包裝與外殼,但傳統(tǒng)上電子設(shè)計人員與機械設(shè)計人員之間鮮有聯(lián)系。要將電子產(chǎn)品放進機械外殼中,過去更多是靠運氣,而非通過良好的管理來實現(xiàn)。 Altium 推出了一款可真正解決這些問題的高效解決方案,能將電子設(shè)計 (ECAD) 與外殼的機械設(shè)計 (MCAD) 工作相互匹配聯(lián)系,徹底改變了現(xiàn)狀。如今,電子

- 關(guān)鍵字: Altium 電子產(chǎn)品 ECAD MCAD FPGA wishbone

DSP在平行雙輪電動車控制系統(tǒng)中的應(yīng)用

- 1 引 言 2001年,美國發(fā)明家Kamen發(fā)明了一種新型的方便快捷的兩輪交通工具“Segway”,行走平衡控制技術(shù)成為全球機器人控制技術(shù)的研究熱點。以平行雙輪電動車作為移動平臺為機器人的研究提供了技術(shù)支持,同時由于他的行為與火箭飛行和兩足機器人有很大的相似性,因而對其運動平衡控制研究具有重大的理論和實際意義。文獻[2]介紹了平行雙輪電動車的控制器電路,以C8051F020單片機為控制核心通過調(diào)整車體平臺的運行位置,從而使車體平臺始終保持平衡狀態(tài)。然而其并沒有考慮載人、載

- 關(guān)鍵字: DSP 平行雙輪電動車 微處理器 單片機 無刷直流電動機

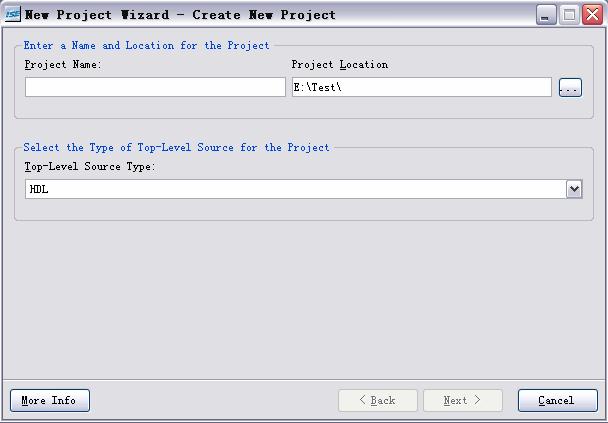

Xilinx FPGA開發(fā)環(huán)境的配置

- 一、配置Modelsim ISE的Xilinx的仿真庫 1、編譯仿真庫: A、先將Modelsim安裝目錄C=Modeltech_6.2b下面的modelsim.ini改成存檔格式(取消只讀模式); B、在DOS環(huán)境中,進入Xilinx的根目錄,然后依次進入bin,nt目錄; C、compxlib -s mti_se -f all -l all -o C:Modeltech_6.2bxilinx_libs。 注意:需要根據(jù)你安裝的modelsi

- 關(guān)鍵字: FPGA Xilinx 仿真 開發(fā)環(huán)境 配置

TI C2000 DSP大獎賽決賽在合肥工大圓滿舉行

- ??????? 本次大賽是TI第一次舉辦C2000系列DSP的大賽,分為自由命題組和TI命題組,吸引了來自合肥工業(yè)大學(xué)、南京航空航天大學(xué)、清華大學(xué)、上海交通大學(xué)、同濟大學(xué)、湖北汽車工業(yè)學(xué)院、北京化工大學(xué)、東北電力大學(xué)等十幾支參賽對伍。C2000 DSP在馬達控制、高速傳感、數(shù)字電源等方面得到了廣泛的設(shè)計應(yīng)用,有些設(shè)計產(chǎn)品已經(jīng)在產(chǎn)業(yè)屆得到了良好的市場反映,如合肥工業(yè)大學(xué)的基于TMS320F2812的配網(wǎng)自動化終端FTU的設(shè)計和實現(xiàn)

- 關(guān)鍵字: 合眾達 TI DSP C2000

dsp+fpga介紹

您好,目前還沒有人創(chuàng)建詞條dsp+fpga!

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司