EEPW首頁(yè) >>

主題列表 >>

dsp+fpga

dsp+fpga 文章 最新資訊

FPGA+DSP實(shí)時(shí)三維圖像信息處理系統(tǒng)

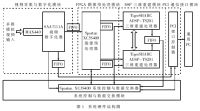

- 三維圖像信息處理一直是圖像視頻處理領(lǐng)域的熱點(diǎn)和難點(diǎn),目前國(guó)內(nèi)外成熟的三維信息處理系統(tǒng)不多,已有的系統(tǒng)主要依賴高性能通用PC完成圖像采集、預(yù)處理、重建、構(gòu)型等囊括底層和高層的處理工作。三維圖像處理數(shù)據(jù)量特別大、運(yùn)算復(fù)雜,單純依靠通用PC很難達(dá)到實(shí)時(shí)性要求,不能滿足現(xiàn)行高速三維圖像處理應(yīng)用。 本系統(tǒng)中,采用FPGA實(shí)現(xiàn)底層的信號(hào)預(yù)處理算法,其處理數(shù)據(jù)量很大,處理速度高,但算法結(jié)構(gòu)相對(duì)比較簡(jiǎn)單,可同時(shí)兼顧速度和靈活性。高層處理算法數(shù)據(jù)量較少、算法結(jié)構(gòu)復(fù)雜,可采用運(yùn)算速度快、尋址方式靈活、通信機(jī)制強(qiáng)大的

- 關(guān)鍵字: FPGA DSP 三維圖像信息處理 EVIP PCI

EDGE手機(jī)基帶處理設(shè)計(jì)的幾種實(shí)現(xiàn)方法評(píng)估

- 在無線市場(chǎng)上,EDGE協(xié)議已迅速為業(yè)者所接受,EDGE手機(jī)設(shè)計(jì)中支持多時(shí)隙傳輸、多種調(diào)制解調(diào)器/語音編譯碼器是基...

- 關(guān)鍵字: EDGE系統(tǒng) 基帶 DSP 語音編碼器 GMSK 形狀因子 算術(shù)邏輯單元 信道質(zhì)量 頻率誤差 音頻電路

基于DSP Builder的14階FIR濾波器的設(shè)計(jì)

- 數(shù)字濾波器在數(shù)字信號(hào)處理的各種應(yīng)用中發(fā)揮著十分重要的作用,他是通過對(duì)采樣數(shù)據(jù)信號(hào)進(jìn)行數(shù)學(xué)運(yùn)算處理來達(dá)到頻域?yàn)V波的目的。數(shù)字濾波器既可以是有限長(zhǎng)單脈沖響應(yīng)(FIR)濾波器也可以是無限長(zhǎng)單脈沖響應(yīng)(IIR)濾波器。在維納濾波器理論發(fā)明的早期,人們使用IIR濾波器,但現(xiàn)在更多是使用FIR濾波器。本文按照Matlab/Simulink/DSP Builder/QuartusⅡ流程,設(shè)計(jì)一個(gè)FIR濾波器。Altera DSP Builder是連接Simulink和QuartusⅡ開發(fā)軟件的DSP開發(fā)工具。在DSP

- 關(guān)鍵字: 濾波器 設(shè)計(jì) FIR Builder DSP 基于

什么是DSP及DSP技術(shù)詳解

- 電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術(shù)中心和交流中心,是電子產(chǎn)品的市場(chǎng)中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡(luò)家園

- 關(guān)鍵字: 數(shù)字信號(hào)處理 DSP

利用Virtex-5 FPGA實(shí)現(xiàn)最低功耗解決方案

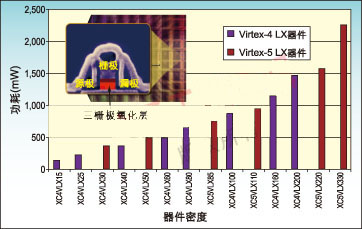

- 過渡至65納米工藝的FPGA具備采用更小尺寸工藝所帶來的優(yōu)勢(shì):低成本、高性能和更強(qiáng)的邏輯能力。盡管這些優(yōu)勢(shì)能夠?yàn)楦呒?jí)系統(tǒng)設(shè)計(jì)帶來激動(dòng)人心的機(jī)會(huì),但65納米工藝節(jié)點(diǎn)本身也帶來了新的挑戰(zhàn)。例如,在為產(chǎn)品選擇FPGA時(shí),功耗的考慮變得越來越重要。很可能下一代設(shè)計(jì)會(huì)需要在功耗預(yù)算不變(或更小)的情況下,集成更多的特性和實(shí)現(xiàn)更高的性能。 本文將分析功耗降低所帶來的益處,還將介紹Virtex-5器件中所采用的多種技術(shù)和結(jié)構(gòu)上的革新,它們能提供功耗最低的解決方案,并且不犧牲性能。 降低功耗的好處

- 關(guān)鍵字: FPGA 低功耗 Virtex-5 靜態(tài)功耗 動(dòng)態(tài)功耗

飛思卡爾推出世界首款軟ColdFire32位內(nèi)核FPGA

- 2008年6月9日,為了滿足高度定制化半導(dǎo)體解決方案的市場(chǎng)需求,飛思卡爾在Altera Cyclone III系列FPGA上推出32位V1 ColdFire內(nèi)核的首款現(xiàn)場(chǎng)可編程?hào)鸥耜嚵校‵PGA)。半導(dǎo)體知識(shí)產(chǎn)權(quán)(IP)許可專家IPextreme公司將通過其在線Core Store™市場(chǎng)免費(fèi)為Cyclone III客戶提供V1內(nèi)核許可。 V1 ColdFire內(nèi)核許可為那些不能通過標(biāo)準(zhǔn)嵌入式處理器和片上系統(tǒng)(SOC)器件解決其設(shè)計(jì)問題的工程師提供一款靈活、經(jīng)濟(jì)高效的解決方案。

- 關(guān)鍵字: 飛思卡爾 FPGA 內(nèi)核 Cyclone

為什么嵌入式開發(fā)人員要使用FPGA

- 電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術(shù)中心和交流中心,是電子產(chǎn)品的市場(chǎng)中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡(luò)家園

- 關(guān)鍵字: FPGA 嵌入式系統(tǒng)

基于DSP多處理器實(shí)時(shí)開發(fā)環(huán)境的設(shè)計(jì)

- 本文通過研究提出了一種多處理器實(shí)時(shí)開發(fā)環(huán)境的設(shè)計(jì)思想,它可以支持多種型號(hào)處理器的同時(shí)開發(fā),使系統(tǒng)級(jí)開發(fā)變得簡(jiǎn)單易行。

- 關(guān)鍵字: 環(huán)境 設(shè)計(jì) 開發(fā) 實(shí)時(shí) DSP 處理器 基于

DSP應(yīng)用系統(tǒng)中的硬件接口電路設(shè)計(jì)

- 介紹了DSP應(yīng)用系統(tǒng)的硬件接口電路:包括電平變換電路、仿真器JTAG接口電路、以及可擴(kuò)展的硬件接口(如A/D、D/A、SRAM)等的設(shè)計(jì)方法,并給出了接口電路在設(shè)計(jì)時(shí)須注意的幾個(gè)問題。

- 關(guān)鍵字: DSP 應(yīng)用系統(tǒng) 電路設(shè)計(jì) 硬件接口

一種基于DSP平臺(tái)的快速H.264編碼算法的設(shè)計(jì)

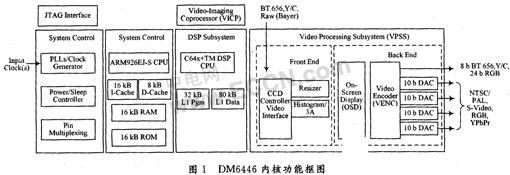

- 視頻壓縮編碼標(biāo)準(zhǔn)H.264/AVC是由ISO/IEC和ITU-T組成的聯(lián)合視頻專家組(JVT)制定的,他引進(jìn)了一系列先進(jìn)的視頻編碼技術(shù),如4×4整數(shù)變換、空域內(nèi)的幀內(nèi)預(yù)測(cè),多參考幀與多種大小塊的幀間預(yù)測(cè)技術(shù)等,標(biāo)準(zhǔn)一經(jīng)推出,就以其高效的壓縮性能和友好的網(wǎng)絡(luò)特性受到業(yè)界的廣泛推崇。特別是在2004年7月JVT組織做了重要的保真度范圍擴(kuò)展的補(bǔ)充后,更加擴(kuò)大了標(biāo)準(zhǔn)的應(yīng)用范圍,但同時(shí)巨大的運(yùn)算量卻成為其廣泛應(yīng)用的瓶頸。考慮到H.264協(xié)議實(shí)現(xiàn)的復(fù)雜度,本文的思路是:一方面提高硬件處理速度和能力,采

- 關(guān)鍵字: DSP 編碼算法 視頻壓縮編碼 編碼器 ARM CPU

Altera為SOPC Builder工具推出32位V1 ColdFire軟核

- 為幫助系統(tǒng)級(jí)設(shè)計(jì)人員在FPGA軟核處理器上有更多的選擇,Altera公司(NASDAQ: ALTR)今天宣布,F(xiàn)reescale將為SOPC Builder工具推出32位V1 ColdFire軟核。為迅速方便的使用Altera® Cyclone® III FPGA建立系統(tǒng)級(jí)設(shè)計(jì),設(shè)計(jì)人員現(xiàn)在使用SOPC Builder工具時(shí),可以選擇Freescale®、ARM®或者Altera軟核處理器以及50多種其他的知識(shí)產(chǎn)權(quán)(IP)模塊。 SOPC Builder是獨(dú)特的A

- 關(guān)鍵字: Altera SOPC Builder 軟核 Freescale FPGA

在采用FPGA設(shè)計(jì)DSP系統(tǒng)中仿真的重要性

- 仿真是所有系統(tǒng)成功開發(fā)的基礎(chǔ)。通過在不同條件、參數(shù)值和輸入情況下對(duì)系統(tǒng)進(jìn)行高級(jí)行為仿真,工程師可以迅速找到、分離并糾正系統(tǒng)的設(shè)計(jì)問題。因?yàn)樵谶@一階段,比較容易區(qū)分設(shè)計(jì)問題和編程問題。通過在系統(tǒng)級(jí)工作,設(shè)計(jì)人員可以確定這一階段的問題是來自設(shè)計(jì)缺陷,而不是編程問題。此外,在信號(hào)處理系統(tǒng)設(shè)計(jì)中使用基于模型的方法大大縮短了“錯(cuò)誤診斷延遲”時(shí)間――從設(shè)計(jì)中出現(xiàn)錯(cuò)誤到發(fā)現(xiàn)錯(cuò)誤并分離錯(cuò)誤的時(shí)間。

- 關(guān)鍵字: 真的 重要性 系統(tǒng) DSP FPGA 設(shè)計(jì) 采用

dsp+fpga介紹

您好,目前還沒有人創(chuàng)建詞條dsp+fpga!

歡迎您創(chuàng)建該詞條,闡述對(duì)dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司