dsp+fpga 文章 最新資訊

FPGA 是實(shí)現(xiàn)綠色搜索技術(shù)的關(guān)鍵

- 無論為數(shù)以百萬計的用戶搜索請求提供服務(wù)還是處理超大量的信息,都需要數(shù)量龐大的計算資源,進(jìn)而消耗大量能源。事實(shí)上,用于計算與冷卻的能耗費(fèi)用是數(shù)據(jù)中心運(yùn)營的最大成本 [1]。隨著數(shù)據(jù)中心的數(shù)量和規(guī)模不斷增長,

- 關(guān)鍵字: FPGA 綠色搜索技術(shù)

基于FPGA的恒溫晶振頻率校準(zhǔn)系統(tǒng)的設(shè)計

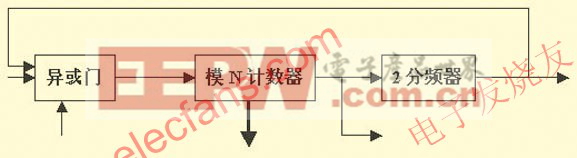

- 摘 要: 為滿足三維大地電磁勘探技術(shù)對多個采集站的同步需求,基于FPGA設(shè)計了一種晶振頻率校準(zhǔn)系統(tǒng)。系統(tǒng)可以調(diào)節(jié)各采集站的恒溫壓控晶體振蕩器同步于GPS,從而使晶振能夠輸出高準(zhǔn)確度和穩(wěn)定度的同步信號。系統(tǒng)中

- 關(guān)鍵字: FPGA 恒溫晶振 頻率校準(zhǔn) 系統(tǒng)

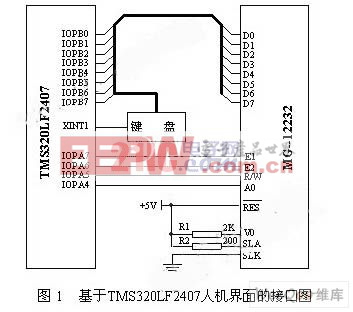

基于DSP芯片TMS320LF2407的人機(jī)界面設(shè)計

- 基于DSP芯片TMS320LF2407的人機(jī)界面設(shè)計, 筆者采用TMS320LF2407作為系統(tǒng)的控制芯片,通過選擇合適的液晶顯示模塊在3V電平構(gòu)建了一個低功耗的中文人機(jī)界面。此中文人機(jī)顯示界面是以TMS320LF2407為核心的運(yùn)動控制系統(tǒng)中的重要組成部分。 一、TMS320LF240

- 關(guān)鍵字: DSP

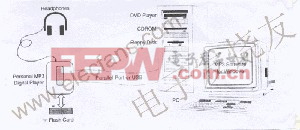

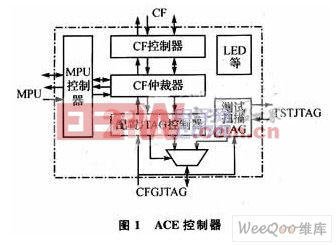

基于System ACE的DSP文件系統(tǒng)設(shè)計

- 基于System ACE的DSP文件系統(tǒng)設(shè)計,引 言 目前,對圖像處理系統(tǒng)的速度和精度要求越來越高,采樣的數(shù)據(jù)量也越來越大。而嵌入式系統(tǒng)中的硬件資源環(huán)境一般比較苛刻,嵌入式微處理器和微控制器的內(nèi)存一般都不大。為了能夠?qū)崿F(xiàn)DSP(Digital Signal Proce

- 關(guān)鍵字: DSP

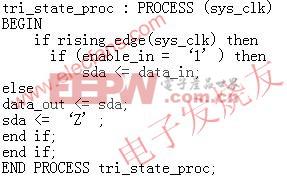

基于VHDL 的矩陣鍵盤及顯示電路設(shè)計

- 摘 要:為了有效防止機(jī)械式鍵盤按鍵抖動帶來的數(shù)據(jù)錯誤,這里在Quartus Ⅱ開發(fā)環(huán)境下,采用VHDL 語言設(shè)計了一種能夠?qū)C(jī)械式4 times;4 矩陣鍵盤的按鍵值依次顯示到8 個7 段數(shù)碼管上的矩陣鍵盤及顯示電路。仿真結(jié)果表

- 關(guān)鍵字: FPGA/ CPLD 鍵盤 電路

賽靈思聯(lián)手四川虹視成立FPGA聯(lián)合實(shí)驗(yàn)室

- 全球可編程邏輯解決方案領(lǐng)導(dǎo)廠商賽靈思公司,2010年9月14日宣布與四川虹視顯示技術(shù)有限公司(簡稱四川虹視)在成都高新區(qū)共同成立FPGA聯(lián)合實(shí)驗(yàn)室, 致力于推動虹視公司最新的OLED產(chǎn)品技術(shù)研發(fā),賽靈思全球消費(fèi)市場總監(jiān)Harry Raftopoulos,高級技術(shù)市場經(jīng)理酆毅,四川虹視總經(jīng)理郎豐偉,技術(shù)總監(jiān)文東星、產(chǎn)品研發(fā)中心部長田朝勇等出席了簽字揭牌儀式。 根據(jù)雙方當(dāng)天簽署的協(xié)議,賽靈思公司計劃向四川虹視提供技術(shù)培訓(xùn),以及多套開發(fā)工具,如Spartan®-6 消費(fèi)視頻開發(fā)套件,Spart

- 關(guān)鍵字: 賽靈思 FPGA

基于FPGA的雙通道旋轉(zhuǎn)變壓器測角系統(tǒng)

- 提出了一種基于FPGA的雙通道旋轉(zhuǎn)變壓器測角電路設(shè)計方案,通過FPGA來控制AD2S82A、AD2S80A的解碼和同步問題。同時用FPGA對轉(zhuǎn)換后數(shù)據(jù)進(jìn)行誤差補(bǔ)償和組合,以及二進(jìn)制角度值的轉(zhuǎn)換,提高了整個系統(tǒng)的集成度和可靠度。整個電路在Altium Designer 9.O設(shè)計環(huán)境下設(shè)計實(shí)現(xiàn)。采用Altera公司的EP2C35F484C6型FPGA芯片進(jìn)行FPGA部分的仿真,實(shí)驗(yàn)和仿真的結(jié)果很好地實(shí)現(xiàn)了該方案的設(shè)計功能,并滿足高精度、高速度轉(zhuǎn)換的設(shè)計要求。

- 關(guān)鍵字: FPGA 雙通道 測角系統(tǒng) 旋轉(zhuǎn)變壓器

基于FPGA的復(fù)數(shù)浮點(diǎn)協(xié)方差矩陣實(shí)現(xiàn)

- 基于FPGA的協(xié)方差矩陣運(yùn)算的實(shí)現(xiàn)大多采用的是定點(diǎn)計算方式,在運(yùn)算過程中,存在數(shù)據(jù)處理動態(tài)范圍小,容易溢出,截斷誤差等問題。加之以空間譜估計為研究背景的協(xié)方差矩陣運(yùn)算,大多得到的是針對特殊陣列模型的實(shí)對稱矩陣,不具備通用性。針對定點(diǎn)運(yùn)算的不足和該運(yùn)算的適用范圍,研究了浮點(diǎn)運(yùn)算和復(fù)數(shù)運(yùn)算的特點(diǎn),提出了基于復(fù)數(shù)矢量的浮點(diǎn)協(xié)方差運(yùn)算的FPGA實(shí)現(xiàn)方案。在Altera\stratix\EP1S20F780C7中的仿真和調(diào)試結(jié)果表明了該方案的有效性。

- 關(guān)鍵字: FPGA 浮點(diǎn) 協(xié)方差矩陣

dsp+fpga介紹

您好,目前還沒有人創(chuàng)建詞條dsp+fpga!

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司