fpga soc 文章 最新資訊

基于FPGA的LDPC編碼設(shè)計(jì)

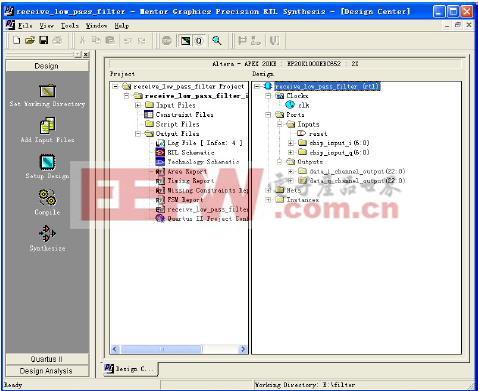

- 針對(duì)低密度奇偶校驗(yàn)碼(簡(jiǎn)稱LDPC碼)的直接編碼運(yùn)算量較大、復(fù)雜度高,根據(jù)RicIlarclson和Urbanke(RU)建議的編碼方案,介紹一種適于在FPGA上實(shí)現(xiàn),利用有效校驗(yàn)矩陣來降低編碼復(fù)雜度的LDPC編碼方案,給出了編碼器設(shè)計(jì)實(shí)現(xiàn)的原理和編碼器的結(jié)構(gòu)和基本組成。在QuartusⅡ7.2軟件平臺(tái)上采用基于FPGA的VHDL語言實(shí)現(xiàn)了有效的編碼過程。結(jié)果表明:此方案在保證高效可靠傳輸?shù)耐瑫r(shí)降低了實(shí)現(xiàn)的復(fù)雜度。這種編碼方案可靈活應(yīng)用于不同的校驗(yàn)矩陣H,碼長(zhǎng)和碼率的系統(tǒng)中。

- 關(guān)鍵字: FPGA LDPC 編碼

基于FPGA的PROFIBUS-DP集線器設(shè)計(jì)

- 摘要:給出了用PROFIBUS―DP HUB來改變現(xiàn)場(chǎng)總線拓?fù)浣Y(jié)構(gòu)的設(shè)計(jì)方案,并對(duì)數(shù)據(jù)轉(zhuǎn)發(fā)方法進(jìn)行比較。描述了DP協(xié)議傳輸?shù)母袷剑攸c(diǎn)介紹并分析了兩種幀結(jié)束檢測(cè)方法及其優(yōu)劣,最后通過八通道DP HUB的實(shí)例來說明了整個(gè)設(shè)計(jì)

- 關(guān)鍵字: 設(shè)計(jì) 集線器 PROFIBUS-DP FPGA 基于

高成本效益的AC感應(yīng)電機(jī)轉(zhuǎn)差控制優(yōu)化方案

- 隨著AC感應(yīng)電機(jī)成為工業(yè)電機(jī)的首選,全方位降低設(shè)計(jì)功耗的需求不斷涌現(xiàn),因此提高這些電機(jī)的效率變得非常重...

- 關(guān)鍵字: FPGA AC感應(yīng)電機(jī)

基于FPGA的多路視頻通道控制

- 根據(jù)織布機(jī)告警系統(tǒng)的需求,提出一種開關(guān)設(shè)計(jì)思想,闡述開關(guān)設(shè)計(jì)過程中遇到的問題以及解決方法。首先在FPGA中設(shè)計(jì)一個(gè)開關(guān)控制信號(hào),利用這個(gè)信號(hào)結(jié)合雙口RAM中的編碼數(shù)據(jù)識(shí)別兩個(gè)撥動(dòng)開關(guān)狀態(tài),從而達(dá)到控制多路視頻通道的目的,使本告警系統(tǒng)更方便的應(yīng)用于實(shí)際工業(yè)中。介紹整個(gè)控制系統(tǒng)的工作原理,給出硬件結(jié)構(gòu)圖和軟件設(shè)計(jì)過程,然后利用QuartusⅡ中的SignalTapⅡLogic Analyzer工具對(duì)控制信號(hào)進(jìn)行實(shí)時(shí)采樣分析,最后在織布機(jī)告警系統(tǒng)中成功實(shí)現(xiàn)視頻通道控制功能。

- 關(guān)鍵字: FPGA 多路 視頻 通道控制

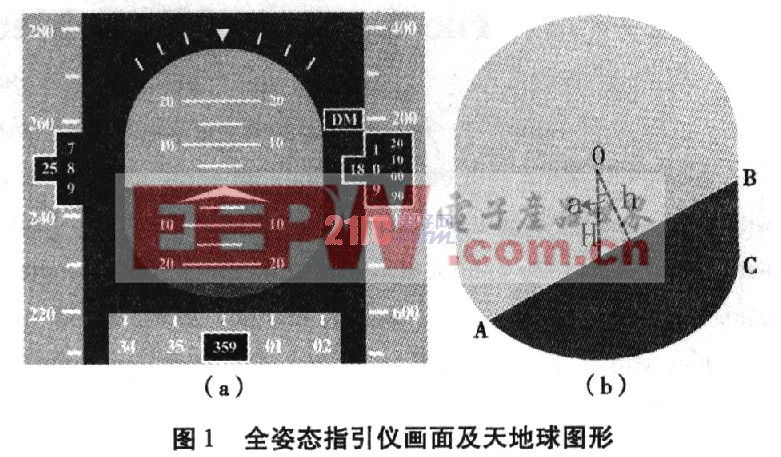

基于DSP與FPGA的全姿態(tài)指引儀圖形顯示系統(tǒng)設(shè)計(jì)

- 基于DSP與FPGA的全姿態(tài)指引儀圖形顯示系統(tǒng)設(shè)計(jì),摘要:針對(duì)機(jī)載電子全姿態(tài)指引儀顯示圖形信息的特征及其變化特點(diǎn),在系統(tǒng)初始化時(shí)將圖形內(nèi)容分為背景層、填充層和動(dòng)態(tài)字符層三層,運(yùn)算過程中只改變根據(jù)參數(shù)變化的填充層和字符層;將圖形運(yùn)算過程分為圖形輪廓生成和

- 關(guān)鍵字: 圖形 顯示系統(tǒng) 設(shè)計(jì) 指引 姿態(tài) DSP FPGA A/D轉(zhuǎn)換

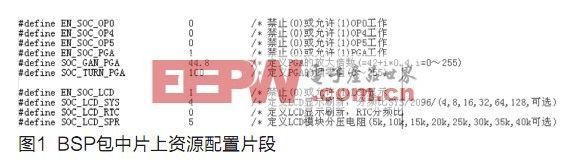

基于時(shí)代民芯SoC的MXT?RTOS51實(shí)時(shí)系統(tǒng)

- 本文論述了在時(shí)代民芯MXT8051高集成度SoC上使用嵌入式實(shí)時(shí)多任務(wù)操作系統(tǒng)的優(yōu)勢(shì),介紹了MXT?RTOS實(shí)時(shí)多任務(wù)操作系統(tǒng)的實(shí)時(shí)、多任務(wù)、面向目標(biāo)板設(shè)計(jì)、模板結(jié)構(gòu)等特點(diǎn)。描述了MXT?RTOS實(shí)時(shí)系統(tǒng)特有的板級(jí)支持包,對(duì)MXT8051片上資源和開發(fā)板的板上資源的支持,實(shí)現(xiàn)了用戶任務(wù)開發(fā)與硬件的無關(guān)性。最后,介紹了MXT?RTOS實(shí)時(shí)多任務(wù)操作系統(tǒng)在時(shí)代民芯MXT8051開發(fā)板上的應(yīng)用實(shí)例。

- 關(guān)鍵字: 時(shí)代民芯 SoC MXT8051 板級(jí)支持包 實(shí)時(shí)操作系統(tǒng)

英特爾在2010年VLSI技術(shù)研討會(huì)上發(fā)布創(chuàng)新成果

- 日前,在美國(guó)夏威夷舉行的2010年超大規(guī)模集成電路技術(shù)研討會(huì)(2010 Symposia on VLSI Technology and Circuits)上,英特爾發(fā)布了多篇重要技術(shù)研究論文,展示了英特爾在計(jì)算創(chuàng)新領(lǐng)域的不懈追求。 1. 可讀懂人腦電波的48內(nèi)核單芯片云計(jì)算機(jī) 想象一下,未來筆記本電腦的視覺功能可媲美人的眼睛,準(zhǔn)確地看到物體的運(yùn)動(dòng)!你可以在網(wǎng)上購(gòu)物時(shí)使用筆記本電腦的3D照相機(jī)和顯示器,并可看到一個(gè)自己的“鏡像”——也就是模擬你

- 關(guān)鍵字: 英特爾 32納米 SoC

Tensilica HiFi音頻DSP成為首個(gè)支持Dolby MS10多碼流解碼器的IP核

- Tensilica今日宣布,Tensilica成為首家采用Dolby MS10多碼流解碼器,用于SoC設(shè)計(jì)的音頻內(nèi)核IP供應(yīng)商。Dolby MS10多碼流解碼器具備多格式音頻解碼技術(shù),在單個(gè)算法包中支持Dolby Digital Plus和Dolby Pulse,用于下一代HDTV(高清電視)、STB(機(jī)頂盒)和DMP(數(shù)字媒體播放器)的設(shè)計(jì)。 Dolby MS10多碼流解碼器對(duì)下一代設(shè)計(jì)是至關(guān)重要的,因?yàn)橛^眾接收到的內(nèi)容信息,不僅僅來源于傳統(tǒng)的廣播和運(yùn)營(yíng)商,而且還來源于互聯(lián)網(wǎng),USB設(shè)備、游戲

- 關(guān)鍵字: Tensilica DSP SoC 多碼流解碼器

fpga soc介紹

您好,目前還沒有人創(chuàng)建詞條fpga soc!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司