DSP/ARM雙核系統(tǒng)的通信接口設計嵌入式系統(tǒng)的核心是嵌入式微處理器和嵌入式操作系統(tǒng)。早期的嵌入式系統(tǒng)...

關鍵字:

ARM DSP 雙核

日前,晶圓代工龍頭企業(yè)臺積電宣布了其一季度業(yè)績,營收為12.9億美元,環(huán)比增長14.1%同比增長16.9%,這一切得益于其不斷進步的工藝制程,就目前28nm制程節(jié)點,臺積電一口氣推出了6款不同規(guī)格的產(chǎn)品,而其他代工廠則表示下半年才會推出28nm的產(chǎn)品。

關鍵字:

Xilinx FPGA

全球領先的硅產(chǎn)品知識產(chǎn)權(SIP)平臺解決方案和數(shù)字信號處理器(DSP)內(nèi)核授權廠商CEVA公司和世界先進的語音通信及移動音頻前端DSP技術開發(fā)商與授權廠商Alango Technologies公司共同宣布,針對CEVA市場領先的CEVA-TeakLite-III?DSP系列產(chǎn)品推出最新的Alango語音處理軟件包。CEVA-TeakLite-III DSP旨在滿足手機設計對更高集成度和更低成本的需求,能夠在單一內(nèi)核中集成無線基帶處理功能與Alango提供的移動音頻、語音和前端語音增強處理功能。

關鍵字:

CEVA DSP

權威的市場分析、領先的技術方案、關鍵元器件展示與講解,2011年4月19日,眾多精彩內(nèi)容伴隨著第四屆中國國際醫(yī)療電子大會(CMET2011)一同亮相深圳。深圳醫(yī)療器械行業(yè)協(xié)會會長陶篤純、藍韻集團產(chǎn)品市場部總監(jiān)劉明宇、中國科學院深圳先進技術研究院 鄭海榮博士分別從深圳醫(yī)療器械產(chǎn)業(yè)發(fā)展概況、醫(yī)改兩年帶來的機遇與挑戰(zhàn)、多學科交叉驅動醫(yī)療儀器創(chuàng)新關鍵等角度出發(fā),

關鍵字:

TI FPGA 醫(yī)療超聲

電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術中心和交流中心,是電子產(chǎn)品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡家園

關鍵字:

煤矸石 DSP 邊緣檢測算法 煤矸石自動分選系統(tǒng)

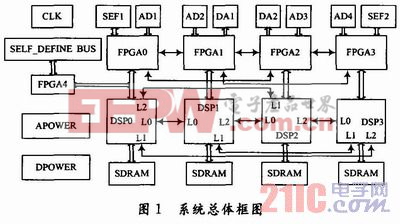

基于FPGA+DSP的高速中頻采樣信號處理平臺的實現(xiàn),摘要:高速中頻采樣信號處理平臺在實際應用中有很大的前景,提出采用FPGA+DSP的處理結構,結合高性能A/D和D/A處理芯片,設計了一個通用處理平臺,并對其主要性能進行了測試。實驗與實際應用表明,該系統(tǒng)具有很強的

關鍵字:

信號處理 平臺 實現(xiàn) 采樣 中頻 FPGA DSP 高速 基于

本心率計在數(shù)字式心率計的基礎上,采用FPGA和VHDL語言實現(xiàn),減少了元器件使用數(shù)量,提高了測量精度和可靠性。該電路能夠實時采集并測量人體心跳的瞬時和平均心跳速率,判斷并顯示心率狀態(tài)(即心跳是否正常、是否過快或過慢、是否有心率不齊現(xiàn)象)。如果心率過快或過慢或者有心率不齊現(xiàn)象,那么將用不同顏色發(fā)光管進行閃爍報警顯示。

關鍵字:

FPGA 數(shù)字式 電路 工作原理

摘要:飛行試驗振動信號具有采樣率高、數(shù)據(jù)量大、處理復雜的特點,在現(xiàn)有條件下,通過遙測鏈路很難將大量的振動數(shù)據(jù)實時傳輸至地面監(jiān)控系統(tǒng)。針對試飛測試的需要,結合某型號的試飛關鍵技術攻關研究,突破試飛振動數(shù)

關鍵字:

POWER FPGA PC 架構

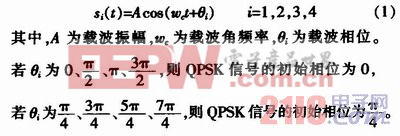

基于現(xiàn)代DSP技術的QPSK調制器的設計,摘要:為了提高DSP系統(tǒng)的開發(fā)效率,引入了現(xiàn)代DSP技術,并由此設計了QPSK調制器。依據(jù)QPSK調制的基本原理,利用MATLAB/Simulink DSP Builder和Quartusll搭建模型,在模塊的形成方式上,采用DSP Builder中的模塊代替

關鍵字:

調制器 設計 QPSK 技術 現(xiàn)代 DSP 基于

DDR SDRAM是Double Data Rate SDRAM的縮寫,即雙倍速率同步動態(tài)隨機存儲器。DDR內(nèi)存是在SDRAM內(nèi)存基礎上發(fā)展而來的,能夠在時鐘的上升沿和下降沿各傳輸一次數(shù)據(jù),可以在與SDRAM相同的總線時鐘頻率下達到更高的數(shù)據(jù)傳輸率。雖然DDR2和DDR一樣,都采用相同采樣方式進行數(shù)據(jù)傳輸,但DDR2擁有兩倍于DDR的預讀取系統(tǒng)命令數(shù)據(jù)的能力。

關鍵字:

Cyclone FPGA DDR2 III

引言 串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)的帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代 。起初, SERDES是獨立的ASSP或ASIC器

關鍵字:

SERDES FPGA 性能 接口

本設計使用硬件描述語言VHDL在FPGA數(shù)字邏輯層面上實現(xiàn)AES加解密,為了系統(tǒng)的擴展性和構建良好的人機交互,設計通過PS/2鍵盤輸入加密密鑰,并將其顯示在LCD上。在軟核MicroBlaze上,通過SPI總線讀寫FIFO和RAM控制射頻芯片CC2420,使系統(tǒng)具有信道選擇、地址識別、自動CRC校驗功能,使系統(tǒng)更加安全、通信誤碼率更低。

關鍵字:

保密 通信 終端 無線 系統(tǒng) Xilinx FPGA 基于

fpga+dsp介紹

您好,目前還沒有人創(chuàng)建詞條fpga+dsp!

歡迎您創(chuàng)建該詞條,闡述對fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。

創(chuàng)建詞條

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473