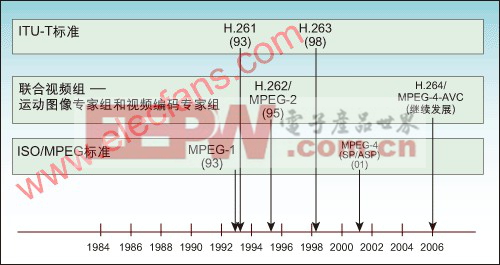

- 嵌入式DSP上的視頻編解碼分析,通用視頻標準和編解碼器

聯合視頻組(Joint Video Team, JVT)由 ITU的視頻編碼專家組(Video Coding Experts Group, VCEG)和ISO/IEC運動圖像專家組(Moving Picture Experts Group, MPEG)組成。VCEG開發自愿性標

- 關鍵字:

分析 解碼 視頻 DSP 嵌入式

- 美國國家標準與技術局(NationalInstituteofStandardandTechnology,NIST)于1997年1月提出發展AES(Ad...

- 關鍵字:

FPGA AES算法 S-box

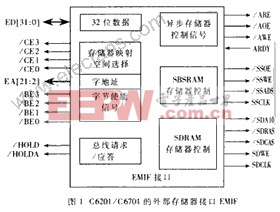

- C6201/C6701 DSP處理器與FLASH存儲器MBM29LV800BA接口技術, DSP是針對實時數字信號處理而設計的數字信號處理器,由于它具有計算速度快、體積小、功耗低的突出優點,非常適合應用于嵌入式實時系統。FLASH存儲器是新型的可電擦除的非易失性只讀存儲器,屬于EEPROM器件,與其它的

- 關鍵字:

MBM29LV800BA 接口 技術 存儲器 FLASH C6701 DSP 處理器

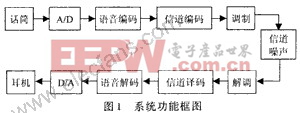

- 現代通信系統與DSP實驗平臺,1 引言 近些年來,通信電子技術和計算機技術發展較快,不斷推陳出新,尤其是無線電通信技術在近幾年得到了迅猛發展。針對日新月異的新技術,大中專院校通信類專業的理論課程及教學方式也需不斷更新,才能跟上時代

- 關鍵字:

實驗 平臺 DSP 系統 通信 現代

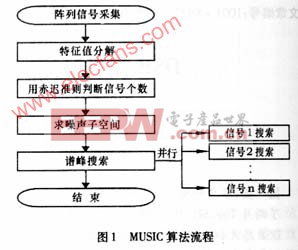

- 基于DSP和FPGA的衛星測控多波束系統設計,一、引言

衛星測控多波束系統主要針對衛星信號實施測控,它包括兩個方面:信號波達方向(DOA)的估計和數字波束合成。波達方向的估計是對空間信號的方向分布進行超分辨估計,提取空間源信號的參數如方位角、仰

- 關鍵字:

系統 設計 衛星 FPGA DSP 基于

- 基于DSP在無刷直流電機控制中的應用,1 概述

本文采用TI公司推出的240XDSP作為無刷直流電機全數字控制核心,組成的伺服系統只需要很少的系統元件。TMS320F240X是美國TI公司推出的高性能16位數字信號處理器(DSP),是專門為電機的數字化控

- 關鍵字:

控制 應用 電機 直流 DSP BLDC

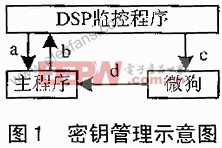

- DSP程序的加密保護體制設計,目前,DSP以其卓越的性能、獨有的特點,已經成為通信、計算機、消費類電子產品等領域的基礎器件。同時,隨著對知識產權的重視,在利用DSP進行產品設計時,如何保護自己的成果,防止破譯者竊取,也成為設計者工作在一

- 關鍵字:

體制 設計 保護 加密 程序 DSP

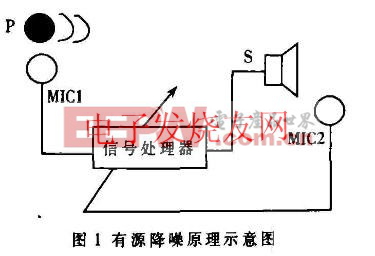

- 基于DSP的有源降噪系統的研究, 在科技迅猛發展的今天,人們在享受現代科技給人類帶來的種種便利之時,也面臨著日益嚴重的污染問題,在這些污染中,噪聲是直接危害人們身心健康的污染源之一。在工業生產、公共交通、宇航、通訊等人類生活的各方面

- 關鍵字:

系統 研究 降噪 有源 DSP 基于

- 針對現有的 RFID 閱讀器具有體積大和不容易升級的缺點,依據 FPGA具有開發簡單,靜態可重復編程和動態在系統編程的特點,研究了基于 FPGA 的 RFID 閱讀器,該種閱讀器具有結構靈活,體積小,升級容易和方便實現不同的外設接口等優點,閱讀器以 FGPA 芯片為核心,實現了 RFID 閱讀器的各種設備接口,采用串口 中斷服務程序接收標簽的數據信息,LCD 顯示標簽的數據信息。在 FPGA 集成開發環境中編譯,調試和綜合, 使用專用下載線將程序下載到 FPGA 芯片中實現其功能。實驗結果表明:FPGA

- 關鍵字:

FPGA RFID 閱讀器

- 本文面向實時圖像采集和處理,采用模塊化設計思想,以TMS320DM642、SAA7115、OSD FPGA等實現了視頻圖像采集和處理系統的硬件電路,該系統電路簡單、結構緊湊、調節靈活、可靠性高、實時性強的特點,通過驗證,滿足設計的應用要求,可為今后視頻圖像采集和處理的進一步研發提供參考。

- 關鍵字:

FPGA 320 642 CCD

- 摘要:為了改變人工神經網絡的研究僅僅局限于算法,只是在通用的串行或并行計算機上模擬實現的現狀,針對函數逼近問題,將BP神經網絡的結構分為3個模塊,采用VHDL語言完成對各個模塊的硬件描述,并使用Altera公司的Q

- 關鍵字:

FPGA 人工神經 網絡系統 實現方法

- 摘要:利用鎖相環進行載波跟蹤是獲取本地載波的一種重要方法,針對鎖相環的噪聲性能和跟蹤速度不能同時達到最優的限制,在鎖相環PLL中引入自適應模塊,根據環路所處的環境自適應對PLL環路參數做出調整。設計中利用仿

- 關鍵字:

FPGA 鎖相環

- 直接數字頻率合成技術(DirectDigitalSynthesis,DDS)是一種從相位概念出發直接合成所需要的波形的新的...

- 關鍵字:

DDS FPGA 數字通信系統

- 基于FPGA的高速卷積的硬件設計實現, 在數字信號處理領域,離散時間系統的輸出響應,可以直接由輸入信號與系統單位沖激響應的離散卷積得到。離散卷積在電子通信領域應用廣泛,是工程應用的基礎。如果直接在時域進行卷積,卷積過程中所必須的大量乘法和

- 關鍵字:

設計 實現 硬件 高速 FPGA 基于

fpga+dsp介紹

您好,目前還沒有人創建詞條fpga+dsp!

歡迎您創建該詞條,闡述對fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473