電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

關鍵字:

DSP 回聲消除 數字音頻處理 網絡通訊

0 引言

關鍵字:

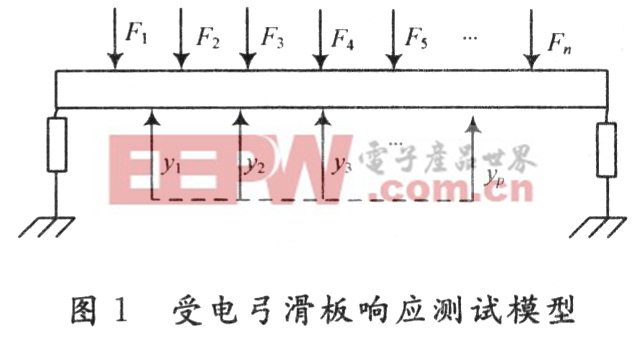

FPGA 激光測速 中的應用

MIL-STD-1553B是一種應用廣泛的航空總線協議,針對總線協議控制器基本依賴于進口專用器件現狀,提出了以Xilinx公司Virtex-II Pro FPGA為核心實現航空總線協議接口的系統設計方案。采用SoPC技術,將PowerPC 405硬核處理器與總線接口邏輯集成在一片FPGA上,從而使系統集成度高、擴展性強。通過測試表明,系統工作穩定可靠.滿足1553B總線協議標準。

關鍵字:

FPGA 航空 總線協議 接口設計

新日本無線開發完成了用于TV和前置多聲道揚聲器系統再現真實自然的立體音響空間的DSPNJU26040-09D。采用了米國SRS Labs, Inc.公司所開發的SRS TruSurround XT的進化新方式: 虛擬環繞聲SRS TruSurround HD/HD4和FOCUS功能。

【開發背景】

近年來地上數字播放DVD?Blu-ray Disc在迅速普及,一般家用5.1ch環繞聲 TV和AV系統也隨之普及。但是一般在家里欣賞5.1ch環繞聲音響時,會有播放設備比較復雜,揚聲器配線繁

關鍵字:

JRC DSP NJU26040-09D 多聲道揚聲器

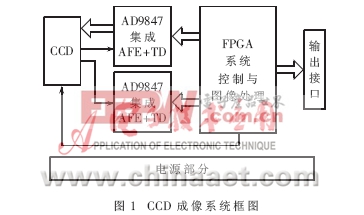

摘 要:利用FPGA和EZ_15SB FX2(CY7C68013)將MT9M112(Sensor)數據準確無損地傳給PC機。方案使用CY7C68013控制器工作在Slave FIFO從機方式,用Verilog HDL語言在FPGA中產生相應的控制信號,最終實現對數據的快速傳輸,

關鍵字:

EZ-USB FPGA FX2 采集

摘 要:在FPGA上實現單精度浮點加法器的設計,通過分析實數的IEEE 754表示形式和IEEE 754單精度浮點的存儲格式,設計出一種適合在FPGA上實現單精度浮點加法運算的算法處理流程,依據此算法處理流程劃分的各個處理模塊

關鍵字:

FPGA 精度 浮點 加法器

摘要:在數字信號處理中經常需要進行乘法運算,乘法器的設計對整個器件的性能有很大的影響,在此介紹20×18比特定點陣列乘法器的設計。采用基4-Booth算法和4-2壓縮的方案,并采用先進的集成電路工藝,使用SMIC O.18

關鍵字:

FPGA 符號 定點乘法器

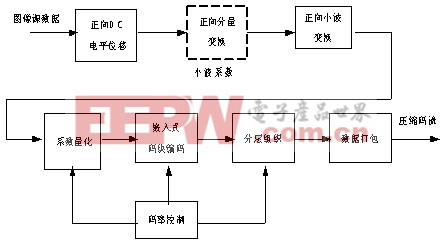

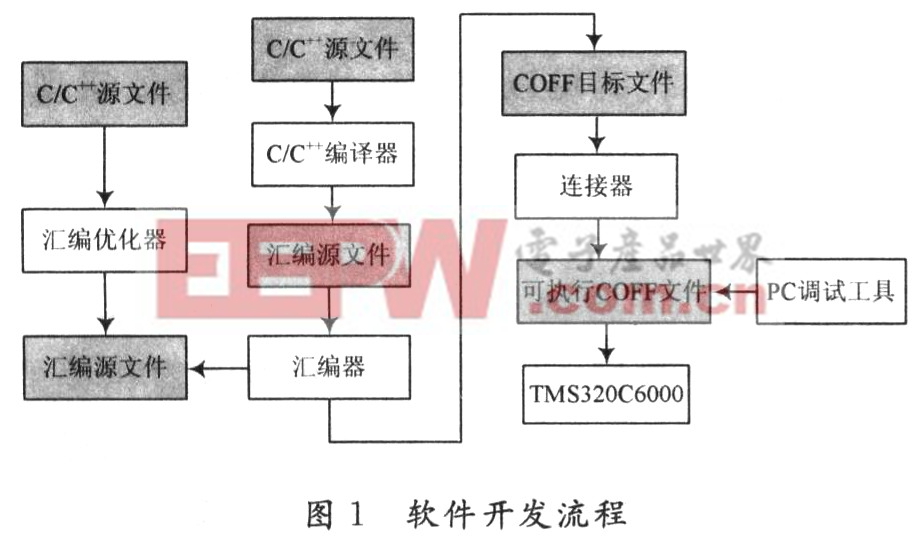

基于TI C6000系列DSP的C/C++程序優化技術,摘 要:在現代DSP的開發中,越來越多地采用C/c++作為開發語言,而C/C++程序的優化成為DSP’軟件開發的重要環節。在此介紹TI C6000的軟件開發流程,重點討論C6000系列的C/C++程序優化技術,包括優化流程,C/C++代

關鍵字:

程序 優化 技術 DSP 系列 TI C6000 基于

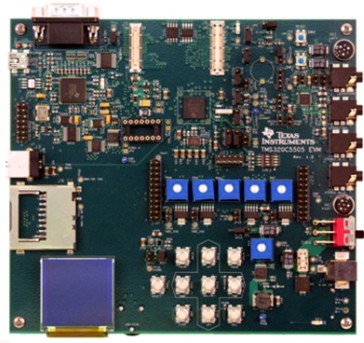

日前,德州儀器 (TI) 宣布推出 TMS320VC5505 與 TMS320VC5504 數字信號處理器 (DSP),其不僅具有業績最佳的待機與工作功耗,而且還可提供高達 320 KB 的片上存儲器以及多個集成外設,從而可將系統成本降低超過 20%,以充分滿足在高級便攜式設備日益普及的情況下,設計人員對選用可延長電池使用壽命、具有更低功耗的解決方案的需求。這兩款 DSP 都具有不足 340uW 的待機功耗與不足 0.3mW/MHz 的工作功耗,可將電池使用壽命延長超過 40%。

運行頻率為

關鍵字:

TI DSP 低功耗 TMS320C550x

fpga+dsp介紹

您好,目前還沒有人創建詞條fpga+dsp!

歡迎您創建該詞條,闡述對fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473