電路板是實現電子電路功能的載體,作為一名電路設計工程師,在產品設計開發階段,您是否遇到過這樣的問題:隨著電子通訊頻率的提高,對PCB線路精度的要求越來越高,擇優選取使得產品可靠性要求越來越高,研發項目需要反復論證修改、電子產品研發周期卻越來越短,電路設計工程師不得不面臨更高的挑戰,如何在最短的時間內快速制作電路板,縮短項目開發時間成為制勝的關鍵之一。

傳統快速制作電路板方法

盡管電路板的制作和加工的方法有很多種,但傳統的快速制板方法主要可分為物理方法和化學方法兩大類:

物

關鍵字:

PCB 電路板

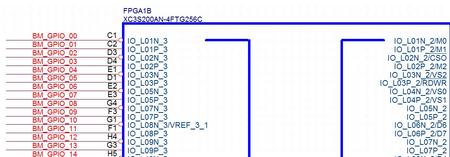

Altera公司今天宣布開始提供非易失MAX® 10 FPGA,這是Altera第10代系列產品中的最新型號。使用TSMC的55 nm嵌入式閃存工藝技術,MAX 10 FPGA這一革命性的非易失FPGA在小外形封裝、低成本和瞬時接通可編程邏輯器件封裝中包含了雙配置閃存、模擬和嵌入式處理功能。MAX 10 FPGA現在已經開始發售,由多種設計解決方案提供支持,這些方案加速了系統開發,包括Quartus® II軟件、評估套件、設計實例,以及通過Altera設計服務網絡(DSN)提供的設計服

關鍵字:

Altera FPGA MAX 10

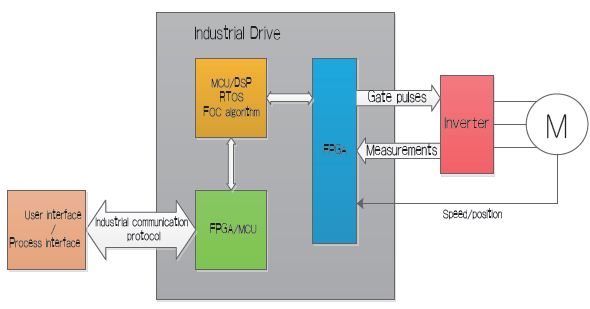

在工業系統中選擇器件需要考慮多個因素,其中包括:性能、工程變更的成本、上市時間、人員的技能、重用現有IP/程序庫的可能性、現場升級的成本,以及低功耗和低成本。 工業市場的近期發展推動了對具有高集成度、高性能、低功耗FPGA器件的需求。設計人員更喜歡網絡通信而不是點對點通信,這意味著可能需要額外的控制器用于通信,進而間接增加了BOM成本、電路板尺寸和相關NRE(一次性工程費用)成本。 總體擁有成本用于分析和估計購置的壽命周期成本,它是所有與設計相關的直接和間接成本的擴展集,包括工程技術成本、安裝和維

關鍵字:

FPGA 電機控制

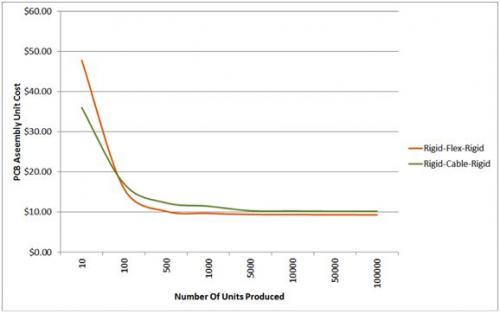

這是一個日新月異的時代。除了創造力和設計能力外,當今的設計人員還面臨著諸多限制,他們需要面對越來越多、日益復雜的設計——一系列通過IO連接的外圍設備。而且,如今的設計越來越追求產品的小型化、低成本和高速度,這些需求尤其體現在移動設備市場。近年來,大量高性能、多功能設備層出不窮,市場發展尤為迅猛,令精明的消費者目不暇接。將這些產品推向電子設計市場需要緊密的設計流程,這通常會涉及到高密度的電子電路,同時還要考慮降低制造時間和成本。

幫助設計師和設計團隊迎接這些挑戰的一個解決方

關鍵字:

軟硬結合 PCB CAD

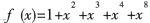

m序列是一種偽隨機序列(PN碼),廣泛用于數據白噪化、去白噪化、數據傳輸加密、解密等通信、控制領域。基于FPGA與Verilog硬件描述語言設計井實現了一種數據率按步進可調、低數據誤碼率、反饋多項式為

的m序列信號發生器。系統時鐘為20MHz,m序列信號發生器輸出的數據率為20~100 kbps,通過2個按鍵實現20 kbps步進可調與系統復位,輸出誤碼率小于1%.

m序列是最長線性反饋移位寄存器序列的簡稱,它是由帶線性反饋的移位寄存器產生的周期最長的一種偽隨機

關鍵字:

FPGA m序列 信號發生器

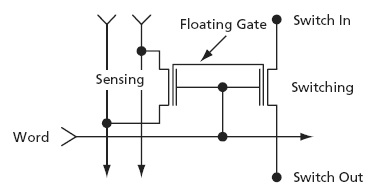

詳細介紹了反熔絲FPGA在提高密碼芯片速度和對密碼算法進行保護方面的應用,并給出了密碼算法芯片中部分模塊的實現方法。

1引言

隨著計算機和通信的發展,信息傳輸過程中信息安全的重要性越來越受到人們的重視。在信息傳輸過程中,人們普遍采用將待傳輸的信息加密進行傳輸,然后在收端進行解密還原信息。對信息的加解密通常采用兩種方法:軟件加解密和硬件加解密。軟件加解密實現簡單,但須對密碼算法進行多重保護存放且加解密速度較慢,而硬件加解密可加快加解密運行速度。在當今信息網絡化的環境下,對加密的速度要求將越來

關鍵字:

FPGA 反熔絲 QUICKLOGIC

去耦電容器的作用你知道嗎?在眾多電路設計的應用中都會用到去耦電容器,但設計者也往往嫌麻煩而省略了去耦電容器的使用。不要小看去耦電容器的使用,它的作用也是不容置疑的。

什么時候要用去耦電容器?它的作用到底是什么?下面我們將考證在不使用去耦器件時會出現什么問題。

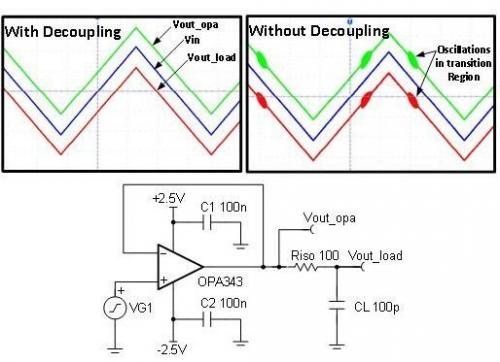

圖1:采用去耦和不采用去耦的緩沖電路(測量結果)

圖1為帶去耦電容器和不帶去耦電容器(C1和C2)情況下用于驅動R-C負載的緩沖電路。我們注意到,在不使用去耦電容器的情況下,電路的輸出信號包含高頻(3

關鍵字:

去耦電容 緩沖電路 PCB

在高密度互聯技術中,PCB規模比較大,需要進行團隊合作,接下來,給大家介紹一種合作開發的方法。

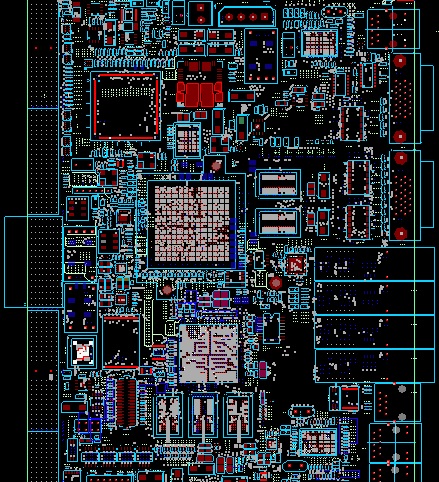

如圖1,為我們需要合作的PCB板。

?

圖1

在圖1的中心部分,有一片比較大的FPGA芯片,如果想將該部分的布局、布線讓另外一個同事處理,自己集中精力把其他部分的搞定。那么該怎么辦呢?點擊place->Design Partition,然后點擊create partition,首先劃定一塊區域。劃定區域的方法有以下幾種:Add rectangle和Add sh

關鍵字:

cadence PCB

有好幾個同事問我cadence之capture中關于保存元器件封裝的問題。

我們知道,封裝庫的管理是非常重要的事情,是我們所有工程設計的基礎,封裝庫有一丁點的錯誤,可能辛苦幾個月的設計就白費了,比如:電源管腳、地管腳定義錯、地址線數據線接反、多定義管腳、少定義管腳等(原理圖封裝如此,PCB封裝也不例外),所以針對比較復雜的元器件,比如FPGA、CPU,動輒上千個管腳,如果自己一個管腳一個管腳畫的話,再加上核對的時間,可能需要一周時間,并且還容易出錯。這時候拿來主義就用到了,別人成熟的封裝,調試沒

關鍵字:

cadence capture PCB

由于航天應用對可靠性提出了更高的要求,這是與一般的FPGA開發最大的不同。當高能粒子撞擊可編程邏輯器件時,撞擊的能量會改變器件中的可配置的SRAM單元的配置數據,使系統運行到無法預知的狀態,從而引起整個系統失效。這在航天設備中是必須要避免的。以FLASH和反熔絲技術為基礎的FPGA與以SRAM為基礎的FPGA相比,在抗單粒子事件方面具有很大的優勢,可靠性高。

ACTEL公司是可編程邏輯解決方案供應商。它提供了多種服務,包括基于反熔絲和閃存技術的FPGA、高性能IP核、軟件開發工具和設計服務,定位

關鍵字:

FPGA FLASH 反熔絲

2014年10月28日-30日,由中華人民共和國工業和信息化部、中華人民共和國科學技術部、上海市人民政府指導,由中國半導體行業協會、中國電子器材總公司、上海市經濟和信息化委員會共同主辦的第十二屆中國國際半導體博覽會暨高峰論壇,將于上海新國際博覽中心N1館盛大開幕。本屆IC China 2014以“應用驅動,快速發展”為主題,通過12500平方米、200余家展商、500余個展位的高規格迎接海內外半導體產業專業觀眾及買家。

9月25日IC China 2014在上海召開展前新

關鍵字:

半導體 集成電路 PCB

Maxim Integrated Products推出Pmod - Arduino適配器(MAXREFDES72#),加速各種量產傳感器的原型開發。MAXREFDES72#可將任何連有Pmod的電路板方便地接入Arduino兼容微控制器平臺。該款適配器采用Maxim業內領先的器件,能夠快速實現物聯網設計,并與更多的數字處理器和應用方便對接。

長期以來,Pmod模塊始終是將專業級外設整合到工程原型開發(尤其是FPGA平臺)的保障。MAXREFDES72#實現了Pmod與Arduino兼容平臺之間的

關鍵字:

Maxim Integrated Arduino FPGA

Altera®公司今天宣布,從2014年9月到11月,將在亞太地區中國、臺灣、韓國、新加坡、馬來西亞和印度的14個城市舉辦Altera 2014年度技術巡展——免費的系列技術研討會。研討會將展示Altera最新的FPGA、SoC以及突破性技術。關于此次系列研討的詳細信息,或者需要注冊參加此次活動,請訪問http://www.altera.com.cn/techroadshow2014。

本年度技術巡展關注的主題是“Silicon Convergence

關鍵字:

Altera FPGA SoC

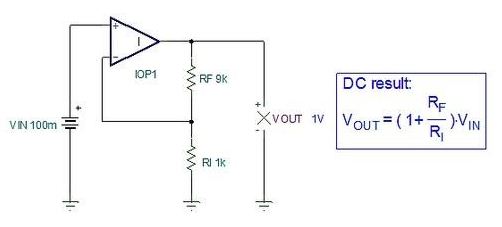

在繪制原理圖時,人們對系統接地回路(或GND)符號總是有些想當然。GND符號遍及原理圖的各個角落,而且原理圖假定不同的GND在印刷電路板(PCB)上都將處在相同的電勢下。事實上,經過GND阻抗的電流會在PCB上的GND連接之間創建電壓差。單端dc電路對這些GND壓差尤其敏感,因為預期的單端電路可轉變為差分電路,導致輸出誤差。

我們以以下所示標準非反相放大器電路為例加以說明。在輸入電源VIN和輸入電阻器RI的GND電勢相等時,適用于我們熟悉的電路增益1+RF/RI。因此,100mV輸入信號乘以10

關鍵字:

GND 差分電路 PCB

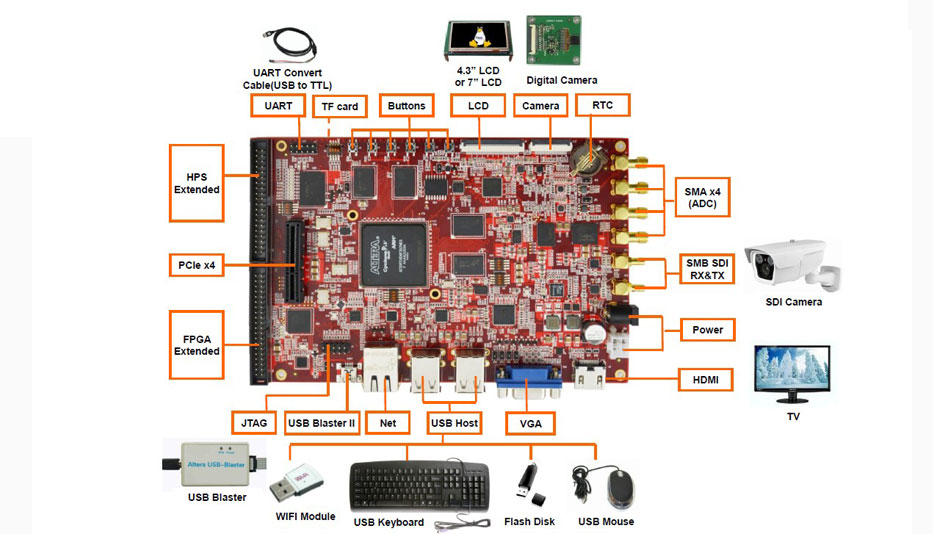

英蓓特科技日前宣布推出基于Altera Cyclone® V SoC的高性能開發板Lark Board。Lark Board專為大容量數據應用的開發而設計,適用于汽車、醫療設備、視頻監控和工業控制等領域。

Altera大中華銷售總監Jeff Li表示:“Lark Board的問世使開發人員能夠更加高效地利用Cyclone V SoC在架構、密度和性能上的優勢,這為他們進行嵌入式系統設計開發提供了一個功能完整且強大的開發平臺。”

Lark Board采用5CS

關鍵字:

Altera SoC FPGA

fsp:fpga-pcb介紹

您好,目前還沒有人創建詞條fsp:fpga-pcb!

歡迎您創建該詞條,闡述對fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473