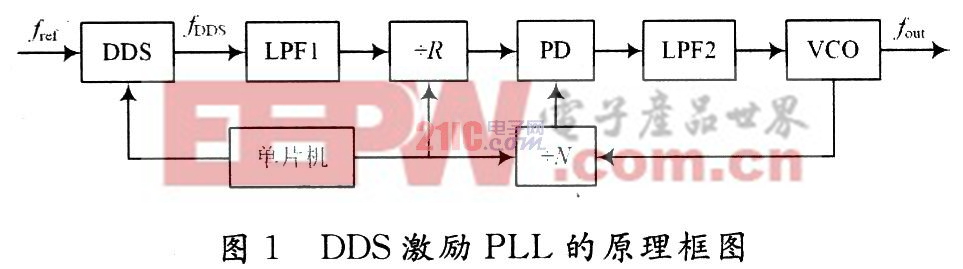

- DDS+PLL高性能頻率合成器的設計與實現,摘要:結合DDS+PLL技術,采用DDS芯片AD9851和集成鎖相芯片ADF4113完成了GSM 1 800 MHz系統中高性能頻率合成器的設計與實現。詳細介紹系統中核心芯片的性能、結構及使用方法,并運用ADS和ADISimPLL軟件對設計方案進行

- 關鍵字:

設計 實現 合成器 頻率 PLL 高性能 DDS

- 摘要:設計一種基于PLL和TDA7010T的無線收發系統。該系統由發射電路、接收電路和控制電路3部分組成。發射電路采用FM和FSK調制方式,用鎖相環(PLL)穩定栽渡頻率,實現模擬語音信號和英文短信的發射。接收電路以TDA701

- 關鍵字:

系統 設計 收發 無線 PLL TDA7010T 基于

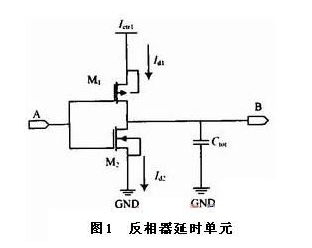

- DSP內嵌PLL中的CMOS壓控環形振蕩器設計,本文設計了一種應用于DSP內嵌鎖相環的低功耗、高線性CM0S壓控環形振蕩器。電路采用四級延遲單元能方便的獲得正交輸出時鐘,每級采用RS觸發結構來產生差分輸出信號,在有效降低靜態功耗的同時.具有較好的抗噪聲能力。在延遲單元的設計時。綜合考慮了電壓控制的頻率范圍以及調節線性度,選擇了合適的翻轉點。 仿真結果表明.電路叮實現2MHz至90MHz的頻率調節范圍,在中心頻率附近具有很高的調節線性度,可完全滿足DSP芯片時鐘系統的要求。

- 關鍵字:

振蕩器 設計 環形 CMOS 內嵌 PLL DSP

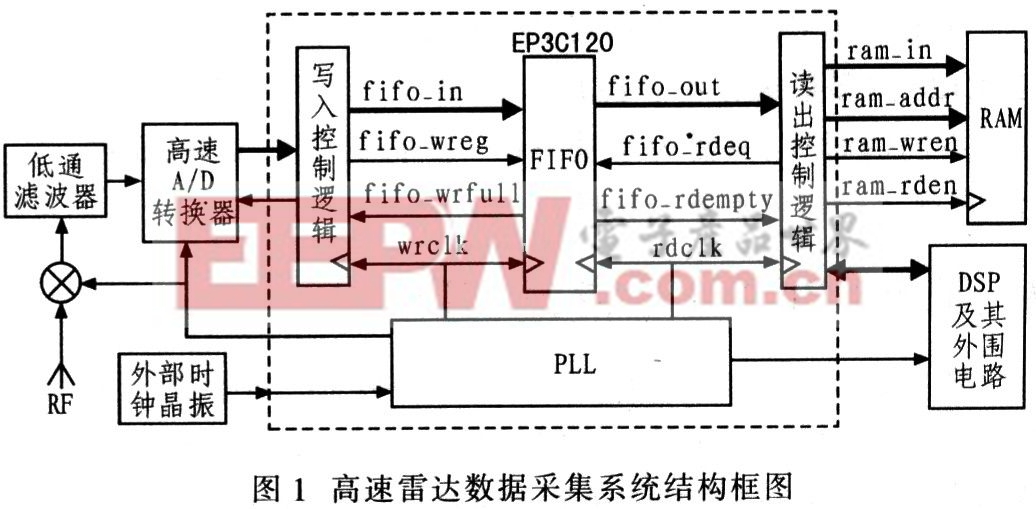

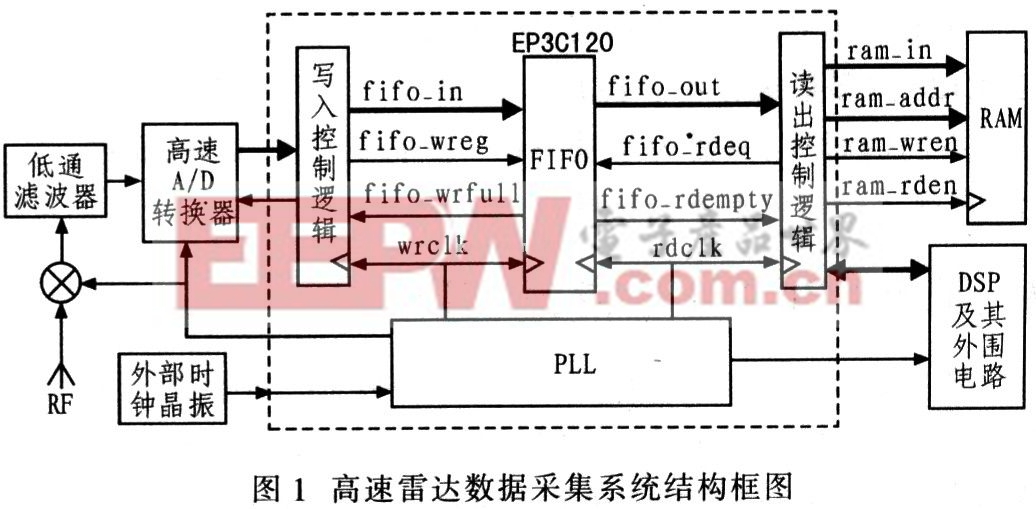

- 異步FIFO和PLL在高速雷達數據采集系統中的應用,將異步FIFO和鎖相環應用到高速雷達數據采集系統中用來緩存A/D轉換的高速采樣數據,解決嵌入式實時數據采集系統中,高速采集數據量大,而處理器處理速度有限的矛盾,提高系統的可靠性。根據FPGA內部資源的特點,將FIFO和鎖相環設計在一塊芯片上。因為未使用外掛FIFO和PLL器件,使得板卡設計結構簡單,并減少硬件板卡的干擾。由于鎖相環的使用,使得整個采集系統時鐘管理方便。異步FIFO構成的高速緩存具有一定通用性,方便系統進行升級維護。

- 關鍵字:

數據采集 系統 應用 雷達 高速 FIFO PLL 異步

- 自動反饋調節時鐘恢復電路設計,0 引言

信息技術的迅猛發展使得人們對數據傳輸交換的速度要求越來越高,因此,各種高速接口總線規范應運而生,從USBl.1到USB3.0,從PATA到SATA,從PCI總線到PCI―Express,其接口總線速度也由最初的Kbyte發展

- 關鍵字:

恢復 電路設計 時鐘 調節 反饋 自動 PLL 時鐘恢復 自動反饋 CDR 高速串行總線

- 三星公司今天宣布,該公司已經成功開發出了全球最薄的Multi-die堆疊封裝技術,將8顆閃存晶片(Die)層疊封裝在一顆芯片內,厚度僅為0.6mm,比目前常見的8層封裝技術厚度降低一半。三星的這項技術最初是為32GB閃存顆粒設計的,將8顆30nm工藝32Gb NAND閃存核心層疊封裝在一顆芯片內,每層晶片的實際厚度僅為15微米,最終封裝完成的芯片才實現了0.6mm的厚度。據稱這樣的超薄大容量閃存芯片可 以讓手機和移動設備設計者在存儲模塊上節省40%的空間和重量。

三星稱,這項層疊封裝新技術的關鍵

- 關鍵字:

三星 封裝 Multi-die

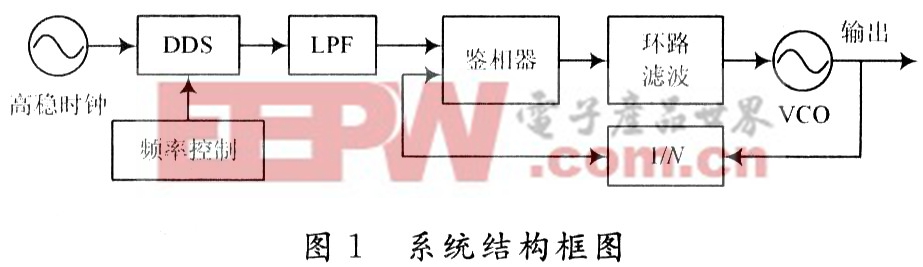

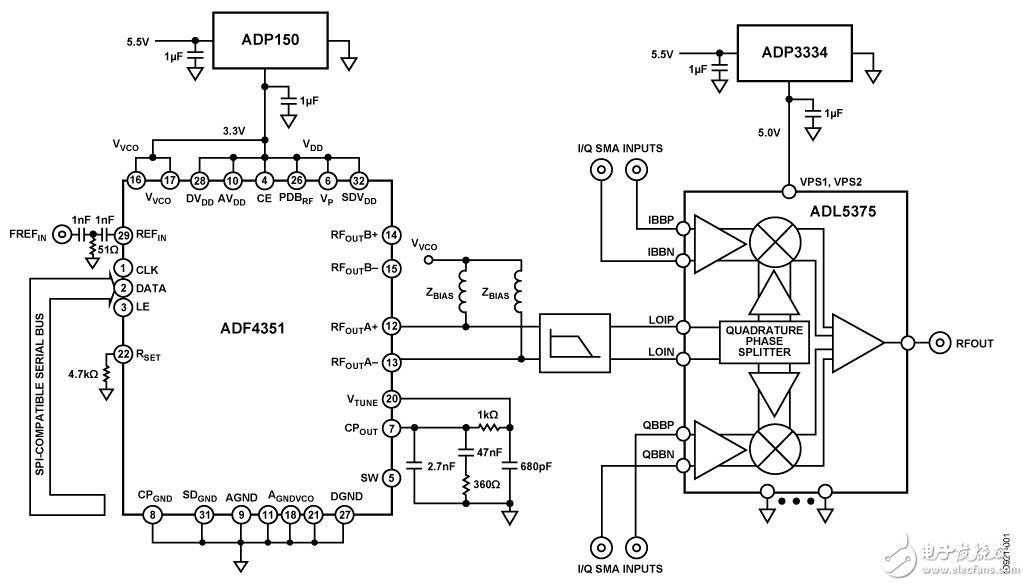

- 由于超寬帶信號的帶寬很寬,傳統的信號產生辦法已不能直接應用于超寬帶通信。為此,提出一種基于DDS+PLL的Chirp-UWB信號產生方案,該方法聯合使用了DDS和PLL兩種信號產生技術,優勢互補。通過ADS結合Matlab對系統的模型建立和性能分析證明,該方案輸出信號性能優良,完全能滿足設計要求,并已成功應用于某超寬帶通信系統。

- 關鍵字:

產生 方案 信號 Chirp-UWB DDS PLL 基于 轉換器

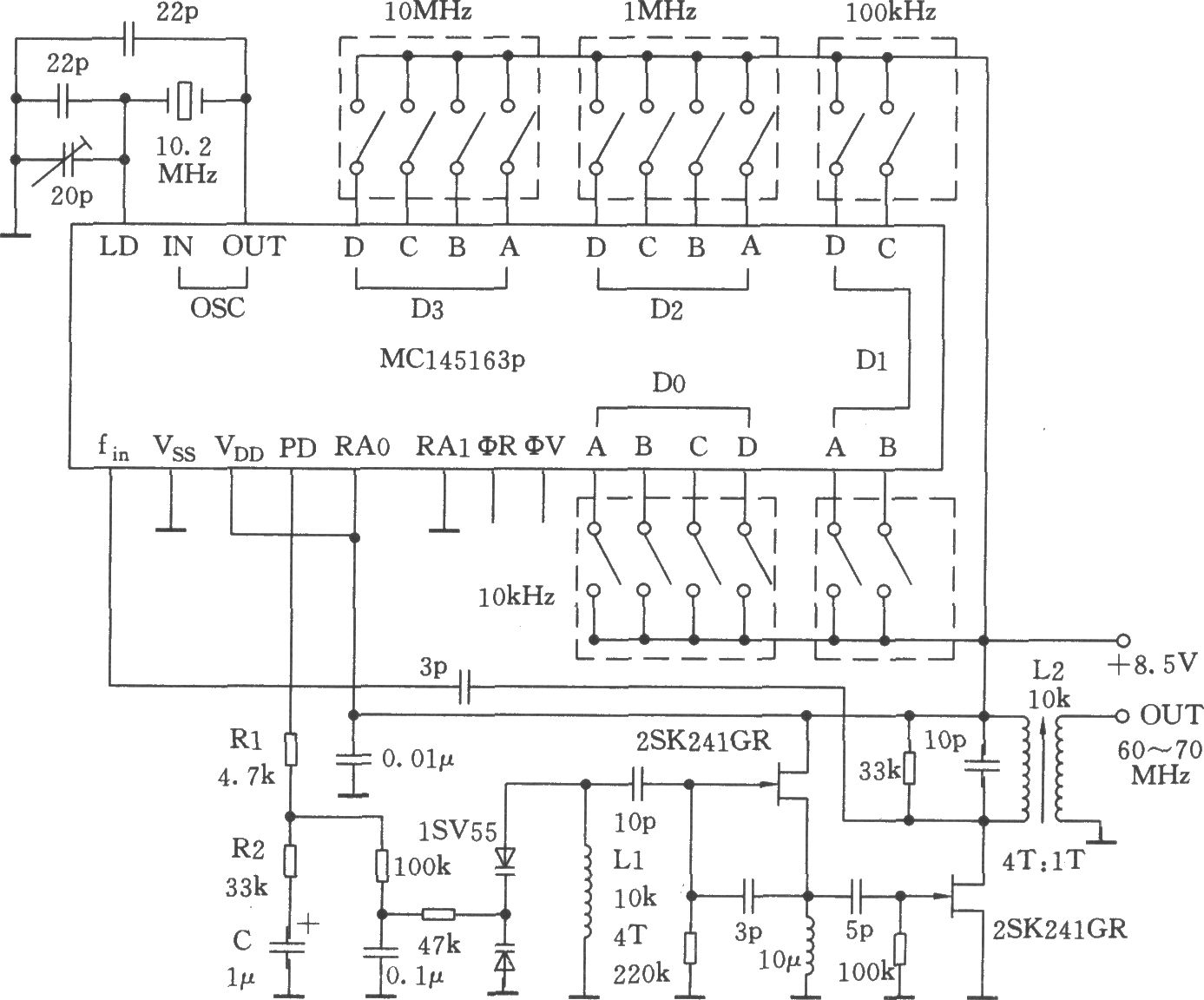

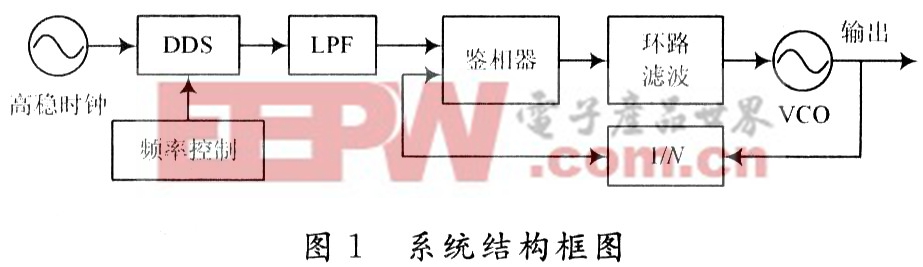

- 頻率合成技術是現代通信的重要組成部分,它是將一個高穩定度和高準確度的基準頻率經過四則運算,產生同樣穩定度和準確度的任意頻率。頻率合成器是電子系統的心臟,是影響電子系統性能的關鍵因素之一。本文結合F

- 關鍵字:

FPGA PLL 頻率合成器

- VSAT是一種小衛星通信系統,可為邊遠地區的家庭和商業用戶提供可靠的、具有成本效應的寬帶數據和其它業務。VSAT采用一種小型天線來發送和接收衛星信號,可為所有處于衛星覆蓋區域內的用戶提供高帶寬連接,無論用

- 關鍵字:

PLL 設計 高頻 單芯片 噪音 基于

- 芯片設計解決方案供應商微捷碼(Magma®)設計自動化有限公司日前宣布,消費電子產品全球供應商Technology Leaders & Innovators (TLi)公司已采用FineSim™ SPICE作為大型模擬IP設計的標準驗證工具。TLi是在對大量商用SPICE仿真產品進行徹底詳盡的評估,結果顯示具有線性多CPU功能的FineSim SPICE提供了較傳統多線程仿真器快上一個數量級的運行時間后才決定選用這款微捷碼軟件。

“我們設計著許多不同類型的

- 關鍵字:

Magma FineSim PLL ADC/DAC 高速I/O

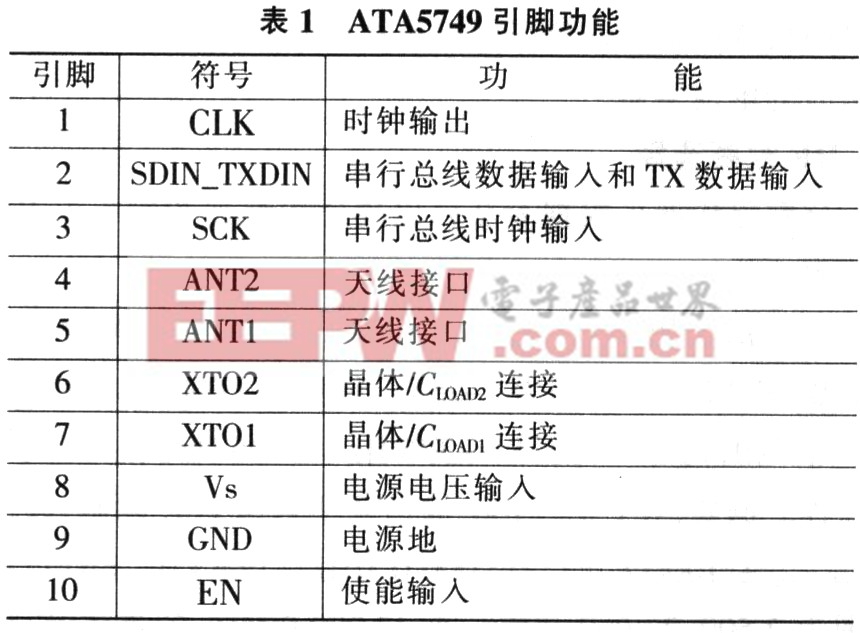

- 概述

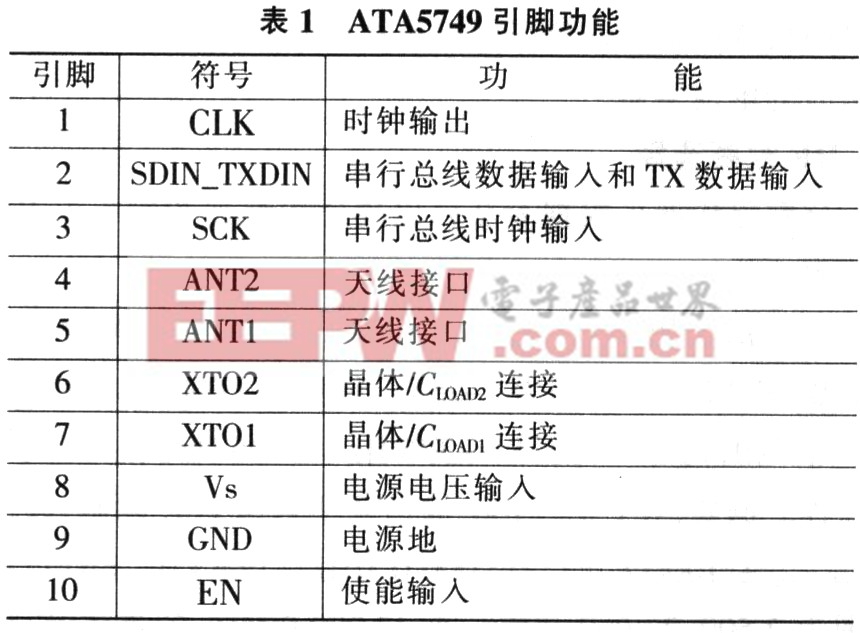

ATA5749是一款集成了完整小數分頻器(fractional-N)的PLL射頻發送器IC,適用于輪胎氣壓計、遙控無鍵入口和被動式入口汽車應用。ATA5749采用幅移鍵控(ASK)和閉環頻移鍵控(FSK)調制,僅使用13.000 0 MHz晶體

- 關鍵字:

分頻 應用 ATA5749 發送 集成 PLL 完全

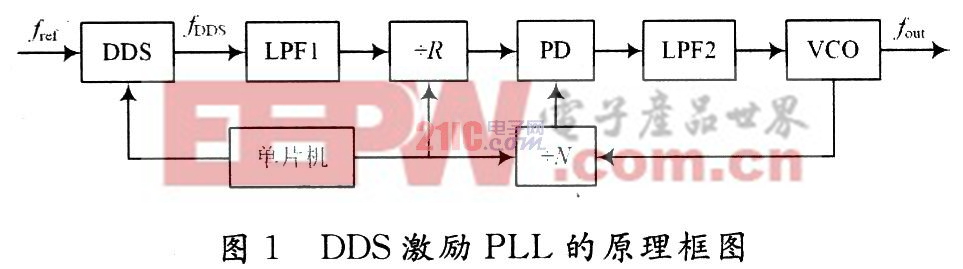

- 現代頻率合成技術正朝著高性能、小型化的方向發展,應用最為廣泛的是直接數字式頻率合成器(DDS)和鎖相式頻率合成器(PLL)。介紹直接數字頻率合成器和鎖相環頻率合成器的基本原理,簡述用直接數字頻率合成器(AD9954)和鎖相環頻率合成器(ADF4112)所設計的本振源的實現方案,重點闡述了系統的硬件實現,包括系統原理、主要電路單元設計等,并且對系統的相位噪聲和雜散性能做了簡要分析,最后給出了系統測試結果。

- 關鍵字:

DDS PLL

- 致力于豐富數字媒體體驗、提供領先的混合信號半導體解決方案供應商 IDT® 公司(Integrated Device Technology, Inc.)推出其 VersaClock™ 計時器件的最新產品系列。VersaClock III 器件是專為高性能消費、電信、網絡和數據通信應用設計的可編程時鐘發生器,可以更經濟有效地在多個晶體和振蕩器之間進行選擇。這些可編程計時解決方案對節省占板空間和保持功效非常關鍵,因其體積可能不允許全定制解決方案。多個具有各種不同需求的系統能夠整合成更少的

- 關鍵字:

IDT VersaClock 可編程時鐘發生器 PLL

multi-pll介紹

您好,目前還沒有人創建詞條multi-pll!

歡迎您創建該詞條,闡述對multi-pll的理解,并與今后在此搜索multi-pll的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473