PHY芯片電路設計

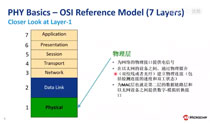

PHY(Physical Layer)芯片是網絡設備中負責物理層功能的集成電路,它完成了OSI模型最底層的工作,即“將數字信號轉換為可在物理介質(如網線)上傳輸的模擬信號”,反之亦然。

PHY芯片原理框圖如圖1:

圖1 PHY芯片原理框圖

以下將從設計要點、核心模塊、接口、PCB布局和調試等方面進行詳解。

1.1. PHY芯片的核心功能與位置理解PHY在系統中的地位。一個典型的以太網系統結構如下:

CPU/MAC (Media Access Control) -> PHY (Physical Layer) -> Magnetics (Transformer) -> RJ45 Connector -> Cable

以太網系統結構示意圖如圖1:

圖2 以太網系統結構示意圖

a. MAC: 負責數據鏈路層,處理數據幀、尋址、錯誤校驗等。通常集成在CPU或交換機芯片中。

b. PHY: 負責物理層。

c. 網絡變壓器: 關鍵無源器件,提供電氣隔離、信號耦合、共模噪聲抑制和阻抗匹配。

1.2. PHY芯片硬件設計核心要點硬件設計工程師需要關注以下幾個核心方面:

1.2.1. 接口定義與連接1) 與MAC的連接接口:

MII: 原始標準,數據位寬4位,時鐘25MHz(用于10/100M)。

RMII: 簡化版MII,數據位寬2位,時鐘50MHz,引腳數少,非常常用。

GMII: 用于千兆以太網,數據位寬8位,時鐘125MHz。

RGMII: 最常用的千兆接口,在GMII基礎上簡化,數據發送和接收各4位(TXD[3:0]/RXD[3:0),使用雙沿采樣(DDR),時鐘頻率125MHz。特別注意:RGMII有發送和接收時鐘時序問題,通常需要在PCB布線時進行延遲匹配,或者使用PHY芯片內部的延遲調整功能。

SGMII: 串行接口,引腳數更少,常用于FPGA連接或高端芯片。

2) 設計要點:

嚴格參考芯片數據手冊的接口定義和時序要求。

RGMII接口的TXC/RXC時鐘線、TX_CTL/RX_CTL控制線和數據線需要做等長布線,誤差通常控制在數百mil(如±500mil)以內,以確保建立和保持時間。

注意接口電壓(如3.3V, 2.5V, 1.8V),如果不匹配,需要電平轉換。

3) 與網絡變壓器的連接接口:

這是PHY的模擬部 分,直接驅動網線。

通常分為電流驅動型和電壓驅動型,連接方式略有不同。

接口通常是差分對:TX+/TX-,RX+/RX-。

1.2.2. 電源設計PHY芯片是數模混合芯片,對電源要求非常高。通常需要多路電源,需單獨供電并避免串擾:

1) 數字核心電源: 為內部數字邏輯供電,電壓最低(如1.0V, 1.2V)。要求低噪聲,通常需要一顆高性能LDO或開關電源(需配合LC濾波)。

2) 數字I/O電源: 為MAC接口(如RGMII)供電,電壓與MAC側電平一致(如3.3V或2.5V)。

3) 模擬電源: 為內部PLL、ADC/DAC等模擬電路供電。這是最敏感、要求最高的電源。必須極其干凈,紋波要小。通常建議使用獨立的LDO,并與數字電源進行磁珠或0Ω電阻隔離。

4) 線路驅動電源: 為發送端的線路驅動器供電,需要提供較大的驅動電流。噪聲也會直接影響發送信號質量。

設計要點:

強烈建議: 為每一路電源使用單獨的穩壓器,尤其是模擬電源和數字電源要分開。

電源去耦至關重要。在每個電源引腳附近放置大小電容組合(如10uF + 0.1uF + 0.01uF),小電容(0.1uF/0.01uF)必須盡可能靠近芯片引腳。

模擬電源部分可以增加π型濾波(磁珠/電感 + 電容)來進一步抑制噪聲。

1.2.3. 時鐘電路參考時鐘: PHY需要一個高精度、低抖動的外部參考時鐘(通常為25MHz)。這個時鐘的質量直接決定了PHY發送和接收數據的時序精度。

時鐘源選擇:

1) 晶體: 需要PHY內部集成振蕩器電路。成本低,但需要注意負載電容的匹配。

2) 有源晶振: 直接輸出方波時鐘信號。性能更穩定,抗干擾能力強,推薦用于要求高的場合。

設計要點:

時鐘線應盡可能短,遠離噪聲源(如開關電源、晶振)。

在時鐘線兩邊布置地線進行屏蔽。

匹配負載電容(如果使用晶體),容值根據數據和晶體規格計算。

1.2.4. 復位與配置優先采用低電平復位,復位信號需保持足夠時長(參考芯片手冊,通常≥10ms),避免復位不徹底。

建議通過 MCU GPIO 控制復位,或使用專用復位芯片,不直接依賴電源上電復位,提升穩定性。

復位電路: 需要一個可靠的上電復位和手動復位電路,確保PHY在穩定電源下啟動。

配置接口:

** strapping引腳**: 通過上拉/下拉電阻在硬件上配置PHY的初始狀態,如設備地址、速度/雙工模式等。

MDIO/MDC: 兩線制管理接口,MAC通過它可以動態配置PHY的內部寄存器、讀取PHY狀態(如鏈接狀態、信號質量等)。這是調試和狀態監控的關鍵接口(MDIO接口最多可以掛載32個PHY設備),MDC(時鐘)和 MDIO(數據)為 PHY 的配置接口,需與 MCU/CPU 連接,走線長度≤10cm。

MDIO 線上拉 1kΩ~4.7kΩ 電阻至 IO 電源,確保空閑狀態穩定;MDC 時鐘頻率不超過 2.5MHz(遵循 IEEE 802.3 標準)。

1.2.5. ESD與防護在網絡變壓器與RJ45連接器之間或之后,可以添加TVS二極管陣列,用于防護來自網線的浪涌和靜電放電。

網絡變壓器本身也提供了一定的隔離和共模噪聲抑制能力。

1.3. PCB布局與布線PHY設計成功與否的重中之重。

1.3.1. 分區布局:將電路板清晰地劃分為:數字區域(MAC接口、數字電源)、模擬/混合信號區域(PHY芯片、時鐘、模擬電源)、高壓/接口區域(變壓器、RJ45)。

區域之間用“壕溝”或不同電源層分割。

1.3.2. 差分對布線:TX+/TX- 和 RX+/RX- 必須嚴格按照差分線規則走線。

等長: 差分對內的兩條線長度差要盡可能小(通常建議<5mil)。

等距: 兩條線從始至終保持相同的間距。

參考完整地平面: 差分對應在完整的參考地平面上方走線,不能跨分割。

阻抗控制: 差分阻抗必須控制在100Ω(對于以太網)。這需要通過PCB疊層、線寬和間距來計算。

1.3.3. 電源分割與去耦:使用電源平面或寬走線為PHY供電。

嚴格遵守數據手冊的推薦,在每一個電源引腳旁邊放置去耦電容。

1.3.4. 接地:推薦使用單點接地或混合接地。將PHY的模擬地和工作地(數字地)在芯片下方通過一個連接點(通常是0Ω電阻或磁珠)連接到主地平面。避免數字噪聲通過地平面干擾敏感的模擬電路。

1.4. 常見問題與規避鏈接不穩定:檢查差分對長度差是否超標,或電源紋波過大,需重新調試電源濾波電路。

無法識別 PHY:排查 MDC/MDIO 接口時序,確保 MCU 輸出時鐘與 PHY 要求匹配,或復位信號時長不足。

雷擊后損壞:未設計防雷電路,需在 RJ45 端口增加 TVS 管和共模電感,且接地路徑阻抗需≤1Ω。

1.5. PHY硬件設計清單接口確認: MAC接口類型、電壓匹配。

電源樹設計: 數字、模擬、I/O電源獨立、干凈。

時鐘源: 25MHz晶體/有源晶振,布局緊湊。

復位與配置: 復位電路可靠,strap引腳上下拉電阻正確。

磁性元件: 選擇與PHY驅動方式匹配的網絡變壓器。

PCB布局: 嚴格分區,數字/模擬分離。

PCB布線: 差分對100Ω阻抗控制、等長、參考地平面完整。

去耦: 所有電源引腳就近放置大小電容組合。

ESD防護: TVS管放置在接口處。

1.5.1. MAC接口類型1) 連接通信方式UTP,PHY對MAC采用的是RGMII、SGMII形式。

圖3 UTP通信

2) 連接通信方式Fiber,PHY對MAC采用的是RGMII形式。

圖4 Fiber通信

3) 連接通信方式UTP/Fiber/RGMII,PHY對MAC采用的是RGMII形式。

圖5 UTP/Fiber to RGMII通信

4) 連接通信方式SGMII to RGMII,PHY對MAC采用的是SGMII形式PHY,對MAC采用的是RGMII形式;

圖6 SGMII/RMGMII通信

5) 連接通信方式Fiber to UTP,PHY對MAC采用的是RGMII、SGMII形式。

圖7

6) 連接通信方式PTP and Sync......,

圖8 PTP and Sync......

1.5.2. PCB設計簡述1) 盡量縮短走線長度,盡量遠離開關電源、晶振等噪聲源,以保證信號質量。

2) USXGMI1、SGMII信號走線必須按 100Q±10%阻抗差分走線;RGMII信號走線必須按 50R±10%阻抗差分走線。

3) 建議在換層孔附近添加回流孔,盡量減少換層過孔數量。

4) 信號走線參考 GND,保證參考平面完整,不建議存在跨平面分割的情況。如果設計中無法避免跨平面參考,建議在跨平面分割處用旁路電容將回流信號連接起來。

5) SGMII信號 100nF 耦合電容建議靠近接收端并對稱放置。

6) SGMII接口 TX/RX 信號之間走線無需等長處理,同層走線時,建議保證 7H 間距。

7) USXGMII接口 TX/RX 信號之間走線無需等長處理,TX 和 RX 建議走在不同層,或者隔開盡可能遠的距離。

8) USXGMII接口建議在扇出時對差分對內P和N較短的走線進行一定的等長補償。

9) RGMII 走線 TX 信號組內等長、RX 信號組內等長,TX 和 RX 間無需等長。

1.5.3. MAC定義說明參考文檔:MII、RMII、GMII、RGMII接口詳解及硬件設計注意事項-CSDN博客

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。