如何在SoC設計中使用事務處理(二)

建模、驗證與調試需要統一標準的符號和框架,以便使架構師和設計工程師能夠協同進行復雜SoC的開發。事務處理級模型(TLM)是進行這種分析的理想模型,在片上系統(SoC)設計中使用事務處理級建模,可讓設計從高效率協同仿真和高產出的分析與調試中受益。

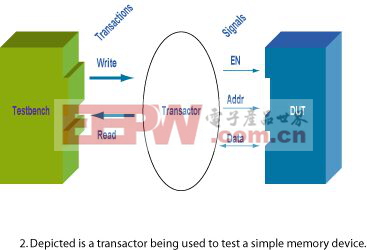

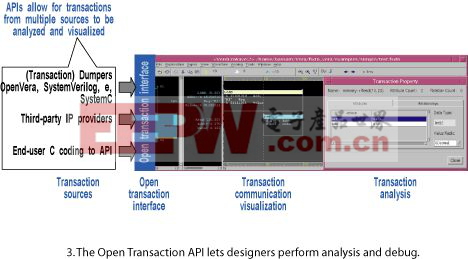

本文引用地址:http://cqxgywz.com/article/148679.htm 下面是對圖2所示的事務處理進行建模的一個簡單代碼段。這個類的旨在于將事務處理數據記錄到作為trans_db instance dump_file類的事務處理數據庫中。輸出被顯示在圖3最右部分。

// Inside program or some other OpenVera context

trans_db dump_file;

trans_stream stream1;

trans_type mem_read;

trans_handle h1;

// open a database file

dump_file=new(test);

// create the memory stream under the test.duv.bus scope

stream1=new(dump_file, test.duv.bus, memory);

// create the read transaction type in the memory stream

mem_read=new(stream1, Read);

// define 2 attributes in the read transaction type

mem_read.create_attr(Addr, INTEGER_DT);

mem_read.create_attr(Data, INTEGER_DT);

delay(10);

// begin a memory read transaction at 10

h1=mem_read.begin_now();

h1.log_integer_attr(Addr, 170);

h1.log_integer_attr(Data, 123);

delay(20);

// end h1 transaction at 20

h1.end_now();

// close the database file

dump_file.close();

|

|

評論