一種FPGA能耗優化的方法設計

實時的電源分析和優化

在不影響產品設計的前提下,使能耗達到FPGA設計的電源的預算要求需要電源分析工具利用一切可能得到的幫助。需要在開發過程中提供很多的信息,使得在原型階段之前就完成最主要的產品設計決定。

從最終產品的角度來看,FPGA的能耗就只是問題的一部分了。電源分析和測試需要擴展到外設電路和支持設備,這樣這些部分才能在開發時不斷修改,以達到能耗優化的目的。

一種實時的方法可以讓FPGA設計達到設計的要求并在最后日期之前完成優化工作。在開始的時候,設想FPGA開發板擁有通過一系列的感應器實時進行電源監控的能力,并將獲得的數據反饋回設計軟件(圖1)。

這樣,電源的實時情況就可以被監視,圖表化并被記錄下來。因為節電模式包括重新編程產生的高峰所產生的能耗可以被精確估計,嵌入式硬件和軟件的選擇就可以被廣泛的開發了。關于能耗的預測則進入了量化的階段。

下一步就是讓最終產品系統,包括開發板和設計軟件獨立于FGPA廠商和器件。這需要開發板具有可插拔和容易交換的FPGA卡板,而且每一個變化的數據都會回復到設計軟件。之后設計軟件可以根據系統驅動結構文件來支持很多不同的FPGA設備,用預先驗證并整合的IP組合來支持所有這些兼容性。

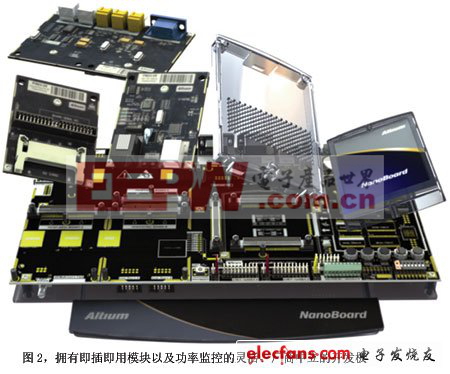

如果軟件系統還包括嵌入式設計的高度抽象捕捉功能,例如原理圖或者圖形流程的界面,就可以使和嵌入式的互動變得更為容易。嵌入式設計可以被容易實現或者被修改,當FPGA設計被改變后電源能耗的變化可以被高級開發板即時的記錄。該開發板還可以涵蓋擁有“智能電源探測器”的子板,記錄所有的硬件實施,以便從功能和電源有效性的角度進行分析(圖2)。

更進一步來說,如果開發板忠實反映產品開發選擇或者甚至目標產品就是開發板,從開發到原型的時間就會大幅的縮短,對于能耗分析預測工具的要求也就不是那么多了。這樣,設計的開發板就可以代替原型,并且在產品開發的過程中精確的執行能耗控制。

有了這樣的方法,你就可以有效地開發最終產品的設計,并可以應用在適合的即買即用或專門定制的板子上。這樣的系統不再需要依靠傳統的能耗預測工具提供精確的數值,相反可以讓用戶可以很方便的在不同的FPGA器件上遷移自己的設計,并迅速探索將嵌入式設計的選擇。

為未來做準備

在目前的設計里激發FPGA的所有特性,特別是在那些電池供電的設備中,意味著對FPGA能耗的完全理解和控制。

FPGA廠商為了迎合市場對低功耗的需求,推出了基于flash的非波動設備,有效能耗架構和高級節電模式。但是不管怎么樣,基于FPGA的設計總會在能耗的有效性和功能之間有所取舍。所以選擇一個合適的工具來平衡這樣的取舍就顯得至關重要。

為了今天和明天的設計,關鍵是要解決如何有效的通過真實快速的原型建立來解決能耗有效性的平衡問題。用戶不能僅僅依靠能耗的預測和分析工具,而要引入先進的設計系統并在硬件上進行實時開發。這樣工程師就可以充分的探索創新的設計來最大限度的激發FPGA的所有特性,并用于開發新一代的節能產品。

評論