DSP與CPLD的智能變電站電網IED設計

需要DSP計算的參數是高壓A、B、C三相電壓、三相電流的有效值,中壓A、B、C三相電壓、三相電流的有效值,各相電壓電流的2~13諧波的幅值和諧波畸變率,以及高中壓三相的功率因素、介損角值。DSP算法要解決的難題是計算出2~13諧波和各相的功率因數。算法的核心是FFT算法。

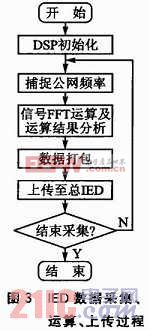

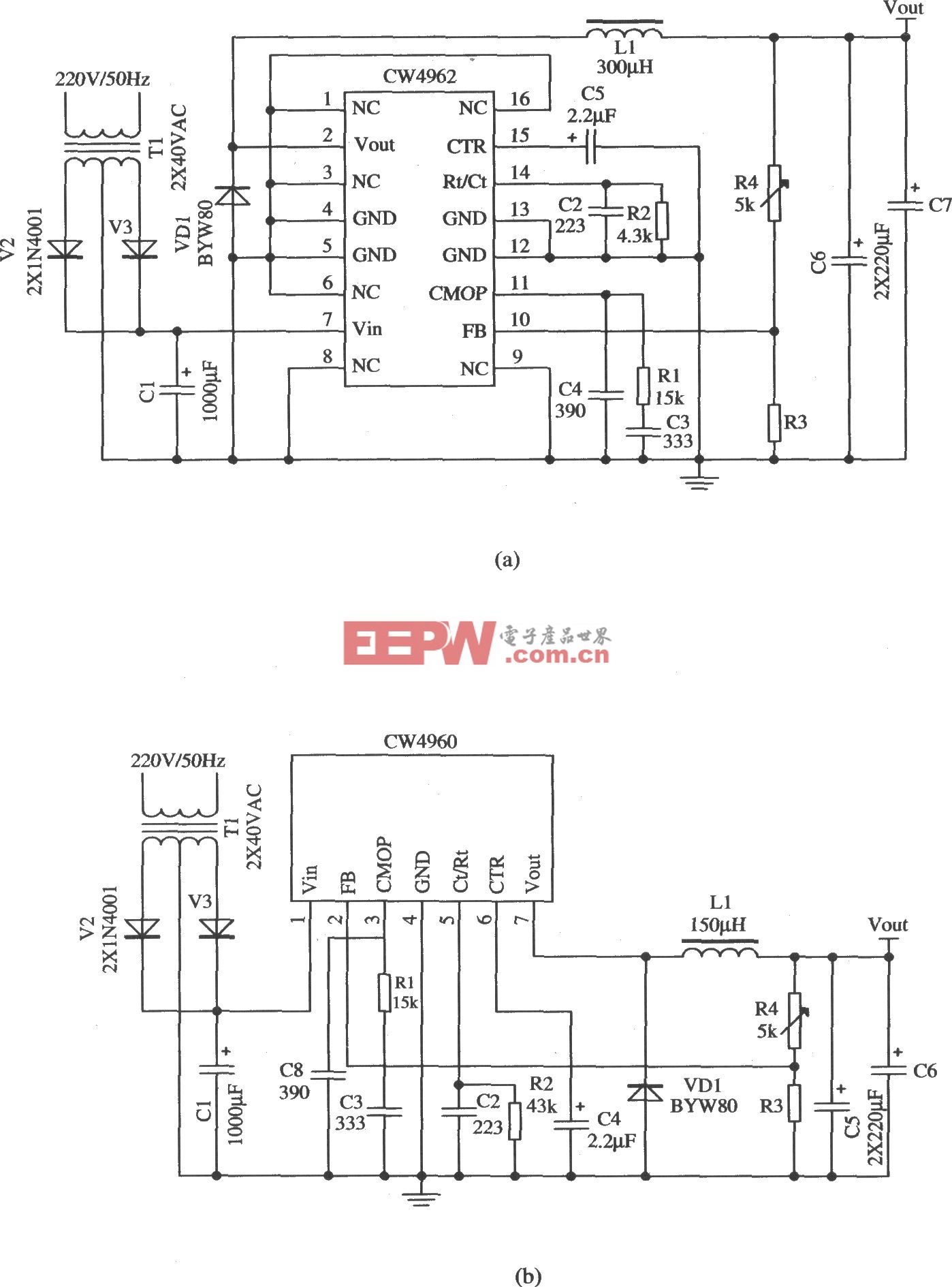

智能電網最少也需要采集20路信號。首先是DSP的相關功能初始化,包括串口、GPIO、EVA事件捕捉模塊和定時中斷。然后通過普通I/O引腳作為觸發信號,依次選擇多路A/D輸入信號,這些信號通過信號調理電路在信號波形穩定后可以經過MAX125被采樣。通過數據總線傳遞給DSP,DSP經過一系列運算后得到功率因素、介損基波諧波含量,并將這些數據按照一定的數據格式打包,通過串口發送到ARM微控制器。AR M再將這些數據傳輸給上位機監控軟件。

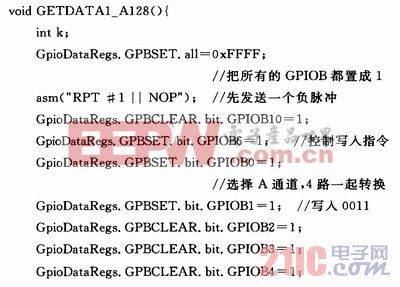

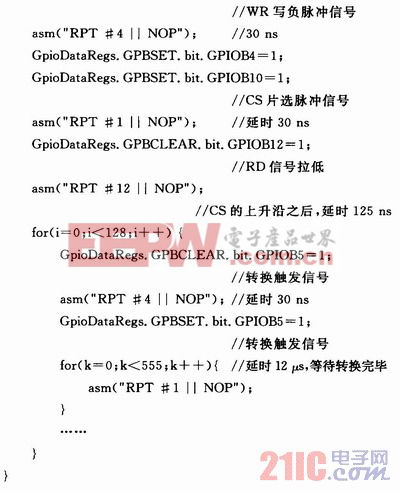

具體代碼如下:

評論