FreeARM7 IP核的微處理器邏輯擴展與驗證

3.2 Bootloader的設置

Bootloader啟動一般分為兩個階段。第一階段主要包含依賴于微處理器的體系結構硬件初始化的代碼,設置堆棧并跳轉到第二階段的C程序入口點,通常采用匯編語言來實現。第二階段通常用C語言完成,以便實現更復雜的功能,也使程序有更好的可讀性和可移植性。在μVision3.63軟件自帶的示例工程“Hello”中,通過下面3行代碼實現了兩個階段的工作交接:

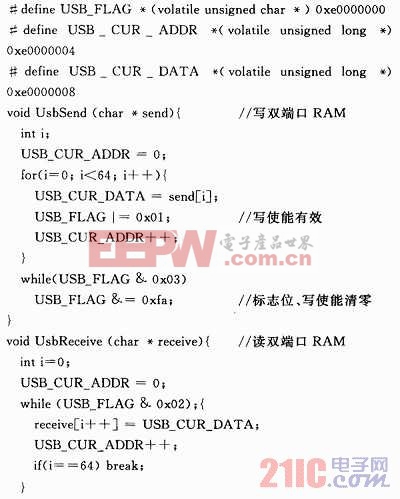

由于本文討論的微處理器只是在FreeARM7基礎之上做了一些基本的擴展,微處理器的體系結構硬件單一,因此第一階段主要是對堆棧位置和大小進行設置。對USB接口的初始化在第二階段的C程序中進行,初始化程序如下:

4 微處理器的功能驗證

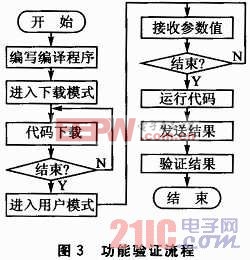

在完成前面的工作之后,借助FPGA對微處理器進行了功能驗證。選用Altera公司DE2開發板作為硬件邏輯的實現載體,微處理器IP核工作時鐘為開發板上27 MHz晶振輸入,USB控制器IP核工作時鐘為27 MHz晶振倍頻至48 MHz。功能驗證流程如圖3所示,在主機上利用μVision 3.63編寫、編譯驗證程序后,微處理器進入下載模式接收主機對設備的代碼下載,之后進入用戶模式接收主機端傳送的驗證程序參數值,在運行代碼后將執行結果返回至主機,通過與主機軟件模擬結果比較達到驗證微處理器運行結果的目的。本文引用地址:http://cqxgywz.com/article/162272.htm

評論