基于FPGA的圖像采集系統設計與實現

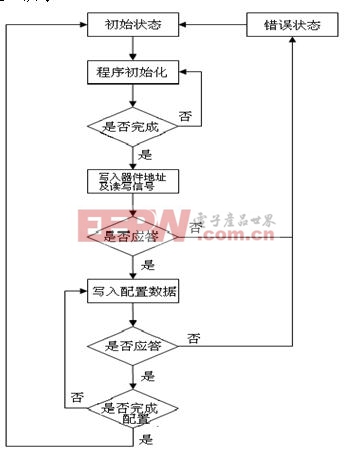

4.1 I2C配置模塊

系統上電后,分別將AD和DA芯片復位,因此需要對它們進行初始化配置。程序將寄存器初始值事先存儲在數組中,設置控制寄存器時,FPGA通過I2C總線按照AD或DA的配置地址、控制寄存器地址、寄存器值的順序依次寫入數據,完成對AD和DA的初始化。I2C的配置模塊的流程[7][8]如圖5所示。

圖5 I2C配置的流程圖

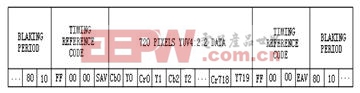

在本系統中,ADV7181芯片輸出8位為CCIR-656格式(也可根據需要配置為16位輸出),它的有效分辨率為720*576,隔行掃描。它輸出的數字視頻數據格式如表1所示。

表1 ADV7181輸出的數字視頻格式表

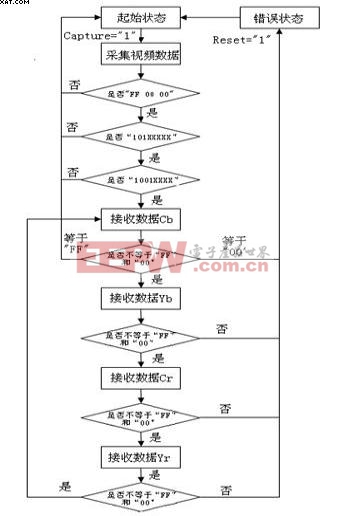

在實際的邏輯設計中,主要的任務就是對CCIR-656格式的行起始標志碼和行結束標志碼的判別與檢測。具體的設計如下:在27MHz像素時鐘信號ADC_LLC的同步控制下,8位的數字視頻數據由ADV7181芯片不斷地輸入到FPGA芯片,FPGA首先檢測“FF 00 00”這三個字節,對于這三個字節的檢測只需要設計一個簡單的有限狀態機即可實現。檢測到上述的三個字節之后,FPGA接著檢測緊隨這三個字節之后的那個未知字節,如果未知字節第4位的值為0,則說明它是SAV字節,如果為1,則說明它是EAV字節。表2為SAV和EAV的數據格式。

表2 SAV和EAV的數據格式表

有了以上的分析可得到如圖6所示的有效視頻數據的采集流程[7][8]圖。

文中按照上述流程設計完成了圖像采集程序,圖7為利用Quartus II自帶的邏輯分析儀工具得到的采集圖像數據波形圖,其中邏輯分析儀的采樣時鐘為27M的ADC_LLC信號,data_in為圖像數據,ad_hs為水平同步信號。

圖6 有效視頻的采集流程

圖7 FPGA采集得到的圖像數據信號

4.3 視頻圖像存儲模塊和DA轉換模塊

由于FPGA內的RAM資源有限,并為了以后擴展方便系統外加了兩片512K*8的SRAM存儲器緩存采集的視頻數據。當一幀圖像采集完成后,FPGA將SRAM中的數據寫入DA轉換芯片,同時開始下一幀的采集。在本系統中視頻編碼芯片接收標準的8位CCIR-656數據,輸出為CVBS復合視頻信號。ADV7177的初始化配置和工作過程與ADV7181類似,這里不再贅述。

5、實驗結果

按照以上設計方案,完成了系統的硬件設計和軟件調試,圖8為系統采集得到的在監視器上顯示的一幅視頻圖像,其中ADV7181采用的是8位CCIR-656輸出格式,ADV7177的輸出格式為CVBS視頻信號。

圖8 系統采集的一幅視頻圖像

6、結論

實驗結果表明,本系統工作穩定可靠,可滿足于高性能的實時圖像處理系統要求。此外,系統采用了FPGA設計方案,集成度高、設計靈活,而且用戶可根據自己的需求進行系統重構,方便快捷,具有較高的應用價值。

評論