單片機89C51與A/D轉換器MAX195的接口設計

3 MAX195的校準

MAX195在上電時自動進行校準。為了減少噪聲的影響,每一個校準試驗進行多次并對其結果求平均值。在時鐘頻率1.7MHz下,校準大約需14000個時鐘周期或8.2ms。除了上電校準之外,把拉至低電平將使MAX195暫停工作,使再次回到高電平便啟動一次新的校準。

注:只有在上電延遲期間,電源尚未穩定就開始上電校準或電源電壓、環境溫度及時鐘頻率發生明顯變化時,才建議重新加以校準。

軟件校準參考子程序如下:

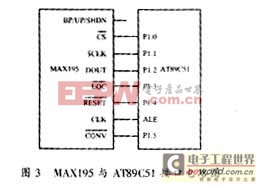

圖中AT89C51的ALE端輸出信號(等于1/6晶振頻率fosc=6MHz)作為CLK變換時鐘。P1.5作為MAX195的啟動控制端。端懸空表示模擬信號可雙極性輸入,也可根據需要接+5V―――單極性輸入;接地―――關閉方式。

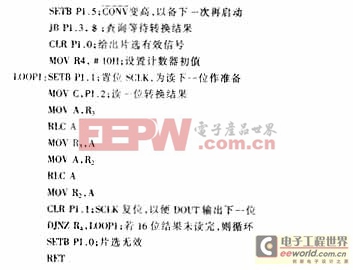

根據圖3,給出A/D采樣程序如下:

注:采樣結果保存在R2、R33中。

評論